## Data acquisition strategies in High **Energy Physics: insights from the Tracker sub-detector of CMS for HL-LHC**

**Giacomo Fedi Imperial College London**

IMPERIAL

27 March 2024

- Introduction: Data acquisition in HEP

- Data acquisition in CMS during LHC upgrade

- •Focus on CMS Tracker

### n in HEP ng LHC upgrade

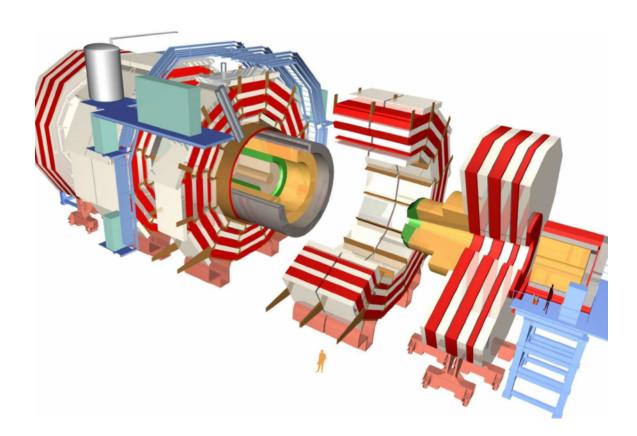

## Large Hadron Collider (LHC)

#### Source: Maximilien Brice, CERN

\_\_\_\_

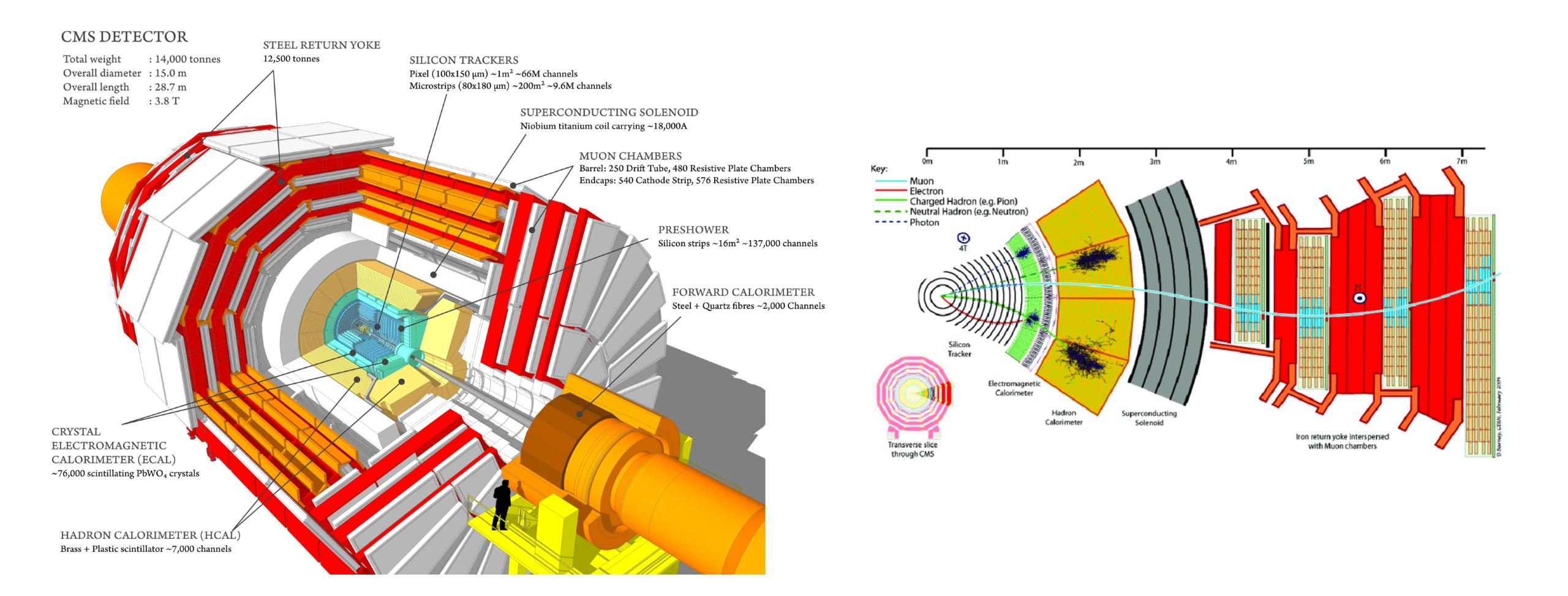

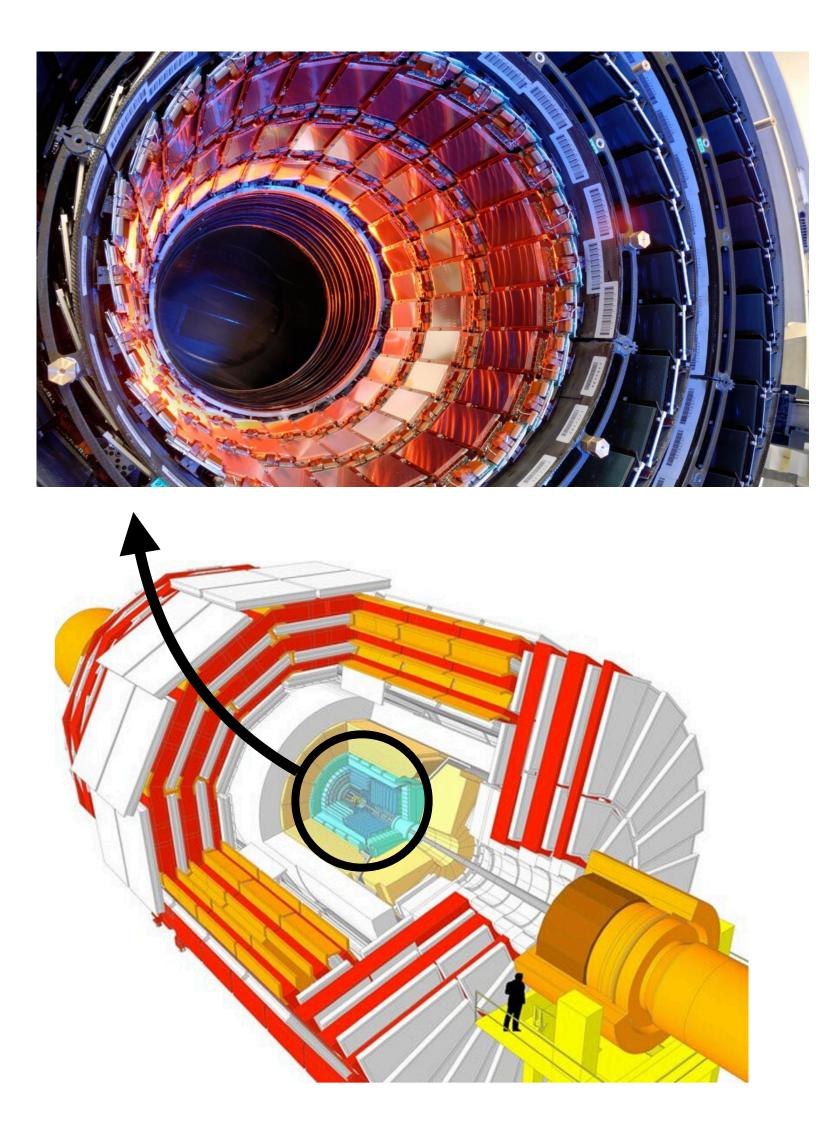

### Compact Muon Solenoid (CMS)

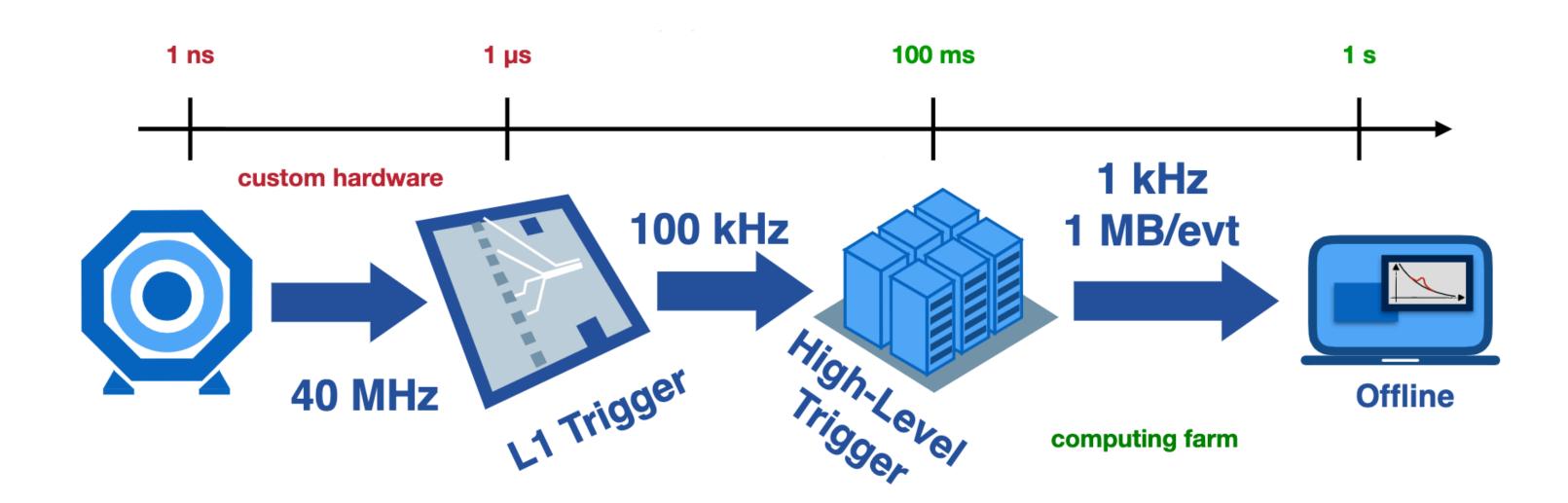

### Nominal bunch crossing rate: 40 MHz Avergage raw event size: ~1MB Data rate: O(100TB/s) Cannot save this amount of data and most of collisions are not interesting -> Solution: Triggering

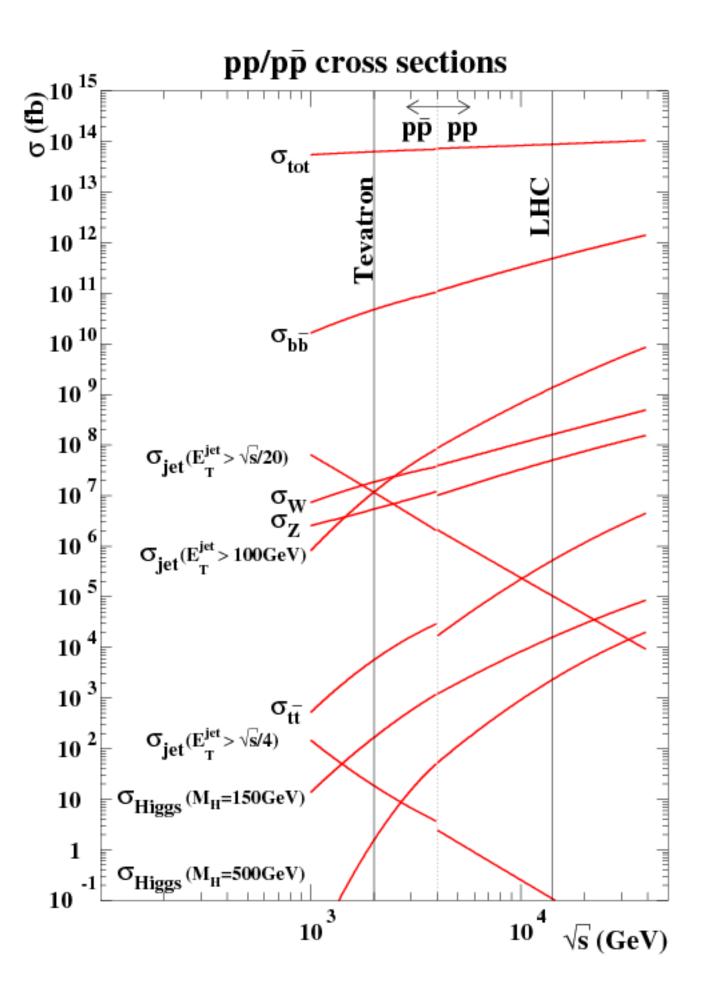

### p-p collisions and cross sections

Source: CMS/Phys. Rep. 426 (2006) 47-358

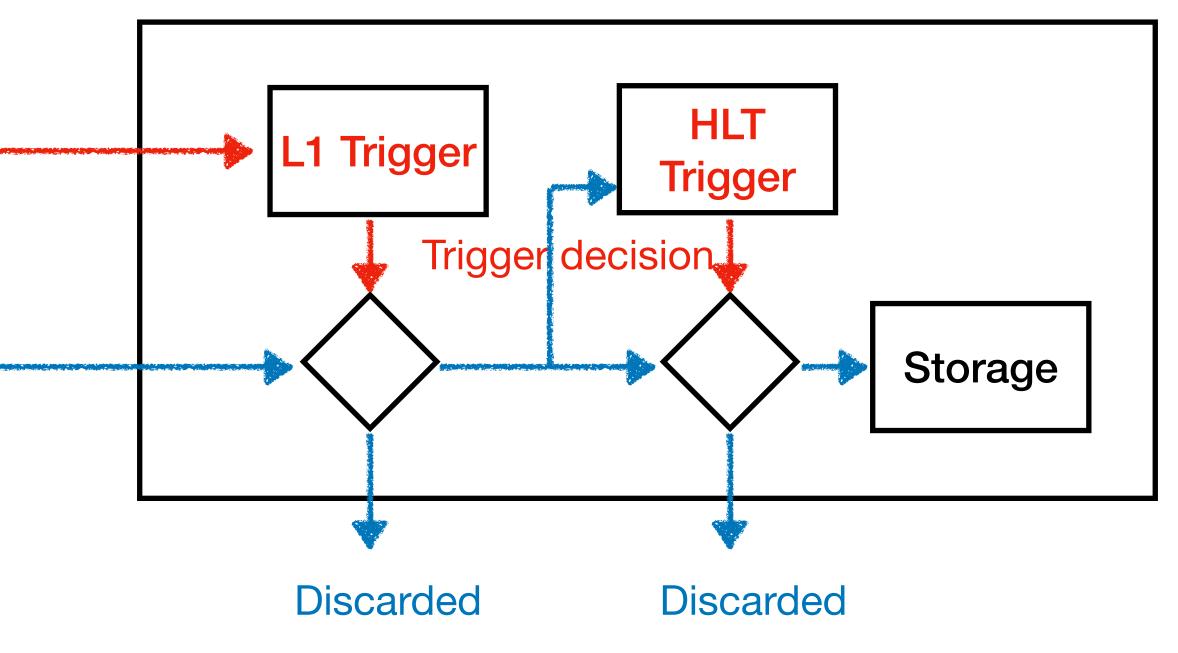

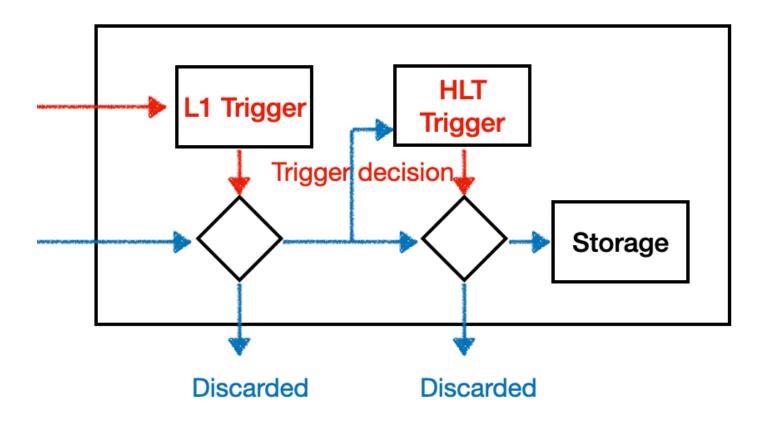

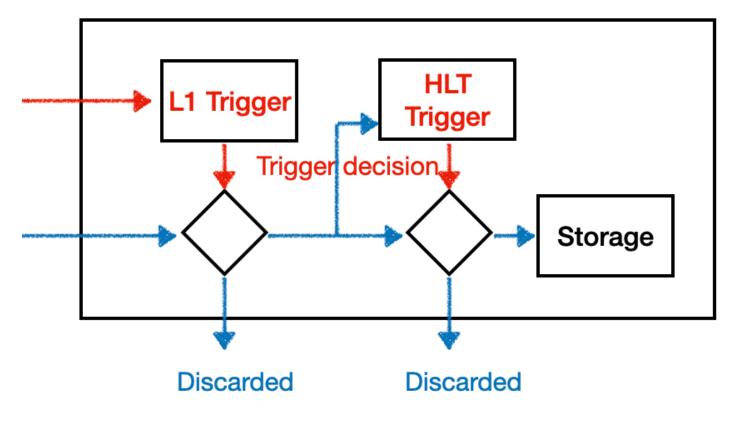

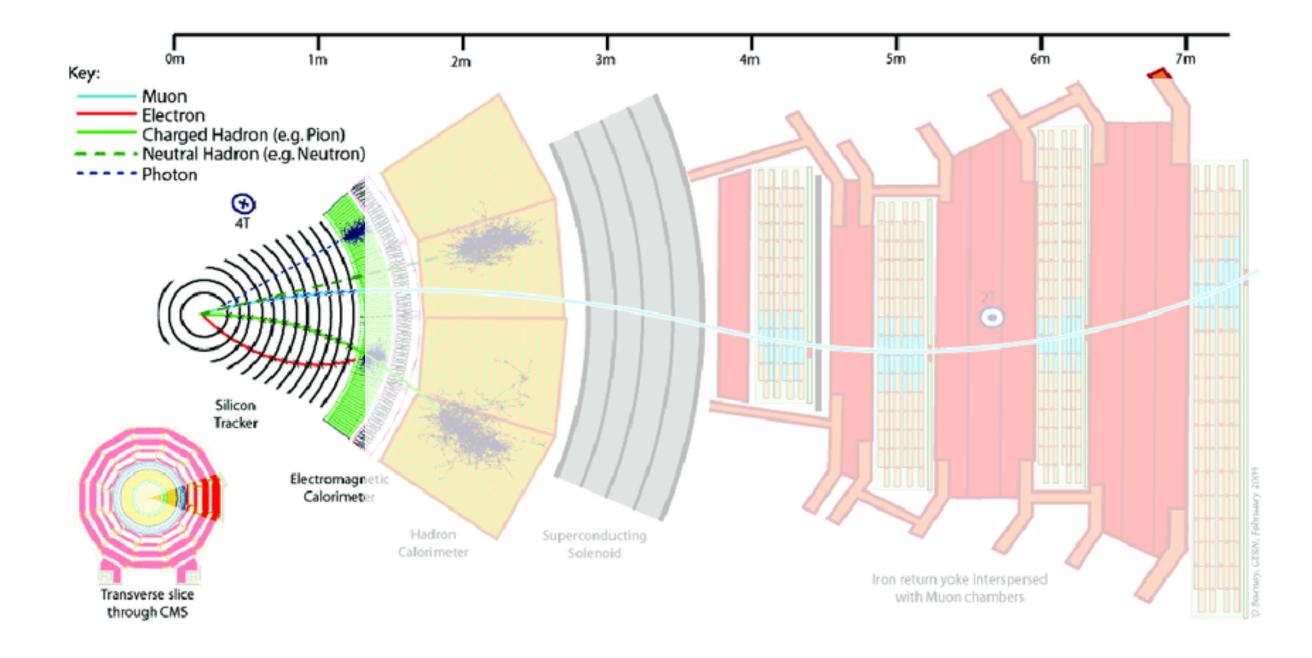

Trigger run very complex physics tests to look for specific signatures, for instance matching tracks to hits in the muon chambers, or spotting photons through their high energy but lack of charge.

- •L1 Trigger: electronics + custom chips + FPGAs processing partial and raw data

- Offline: fine grained physics object reconstruction

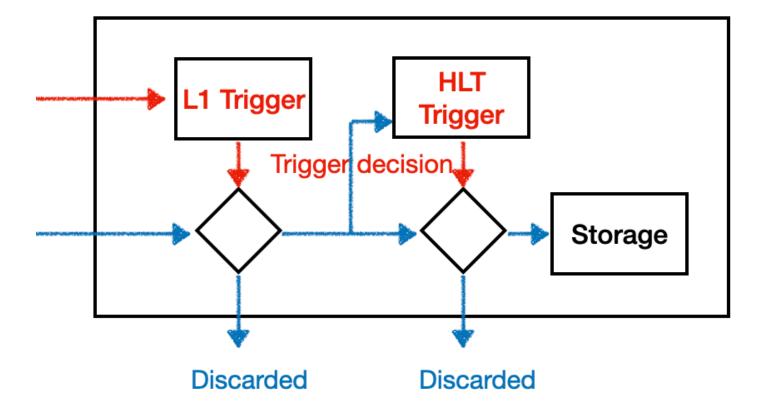

## Triggering

• High-Level Trigger: PC farm processing the full data obtaining good resolution physics objects

- Trigger path: for event selection

- Data path: data sample, data collection, and storage of the selected events

Subdetectors

Trigger path Partial/low res data

Data path Full resolution data

Variations: LHCb recently introduced a trigger less readout; no need for hardware trigger

Simplified and generic Trigger and DAQ schematics

- Selects based on raw data from the sub detectors and a coarse granularity information

- Fast, based on custom electronics (front-end part) and FPGAs

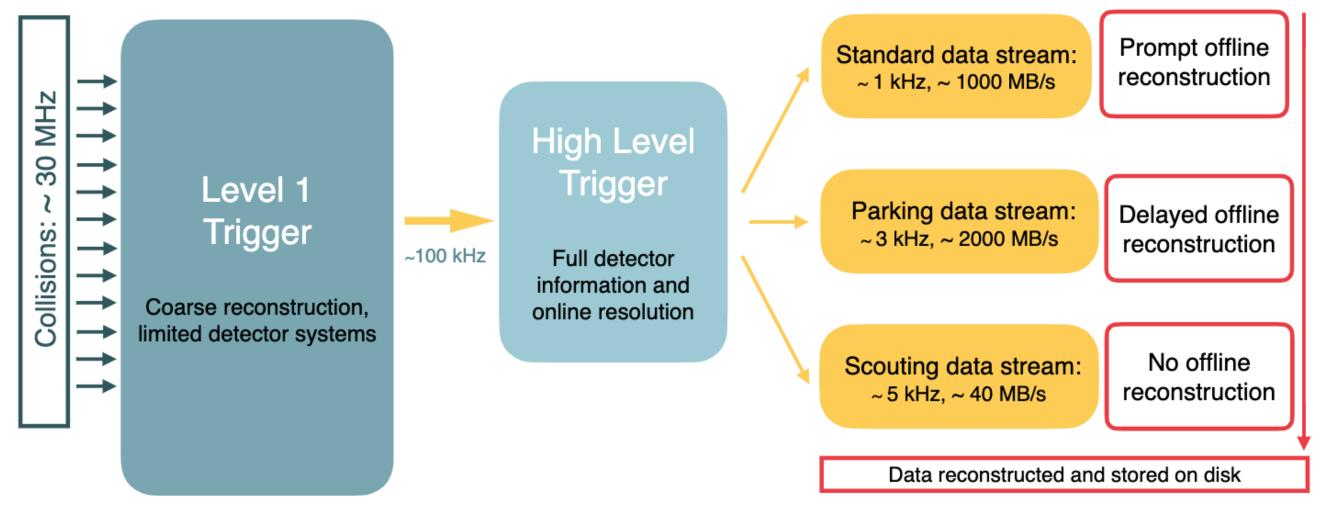

- In the current detector it accepts events at a rate of about 100KHz (**rejecting 99.75%** of events)

- Multiple trigger "path" are implemented in order to select **physics** "objects" such as photons, electrons, muons, jets, missing E<sub>T</sub> Information based on the muon chamber sub-detector and energy

- deposits in the calorimeters

- Each path can be based on multiple objects, e.g. double photons to trigger on Higgs->γγ

## High Level Trigger (HLT)

- Selects based on the full detector data with a **good granularity**, but often less granular than the offline object reconstruction

- Relatively slow O(100) ms process done in PC farms

- In the current detector it accepts events at a rate of about 1KHz (rejecting 99% of events)

- Multiple trigger "path" are implemented in order to select **physics** "objects" such as photons, electrons, muons, jets, missing  $E_T$  and their correlations

- Try to find the signature of interesting **physics processes**, e.g. Higgs decays, top decays, beyond the Standard Model particles, etc

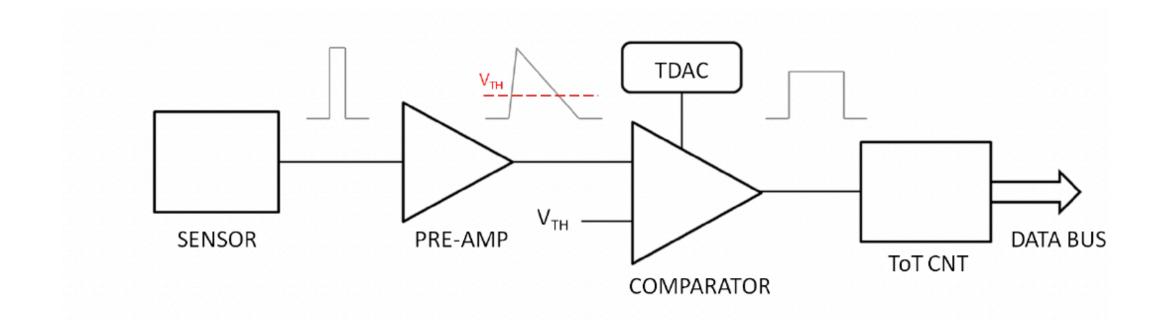

- Data collection starts in the electronics of the sub detectors • Signals from sensitive material (calorimeter crystals + PMT, tracker silicons, etc) is **readout**

- Data is sent to the "back-end" electronics in case the L1 trigger gives the green light

- Data from each sub detector is routed by a commercial switched **network** to combine all the sub detector info

- Data is used by HLT to make the last trigger decision

- Data with HLT green light is saved into local storage

- Data is used for the offline event reconstruction and distributed to multiple data centres - Grid - for data analysis

### **Alternative ways of DAQ**

### Data scouting

- Reduced the event size by saying HLT information

- Avoids the HLT data buffering bottleneck

### Data parking

- Exploits the computational margin arising from the LHC fill luminosity decay

- Event are reconstructed later in time (normally "prompt" reconstruction is done after 48h) and saved on tape

- Avoids the reconstruction resources bottleneck

#### arxiv2403.16134

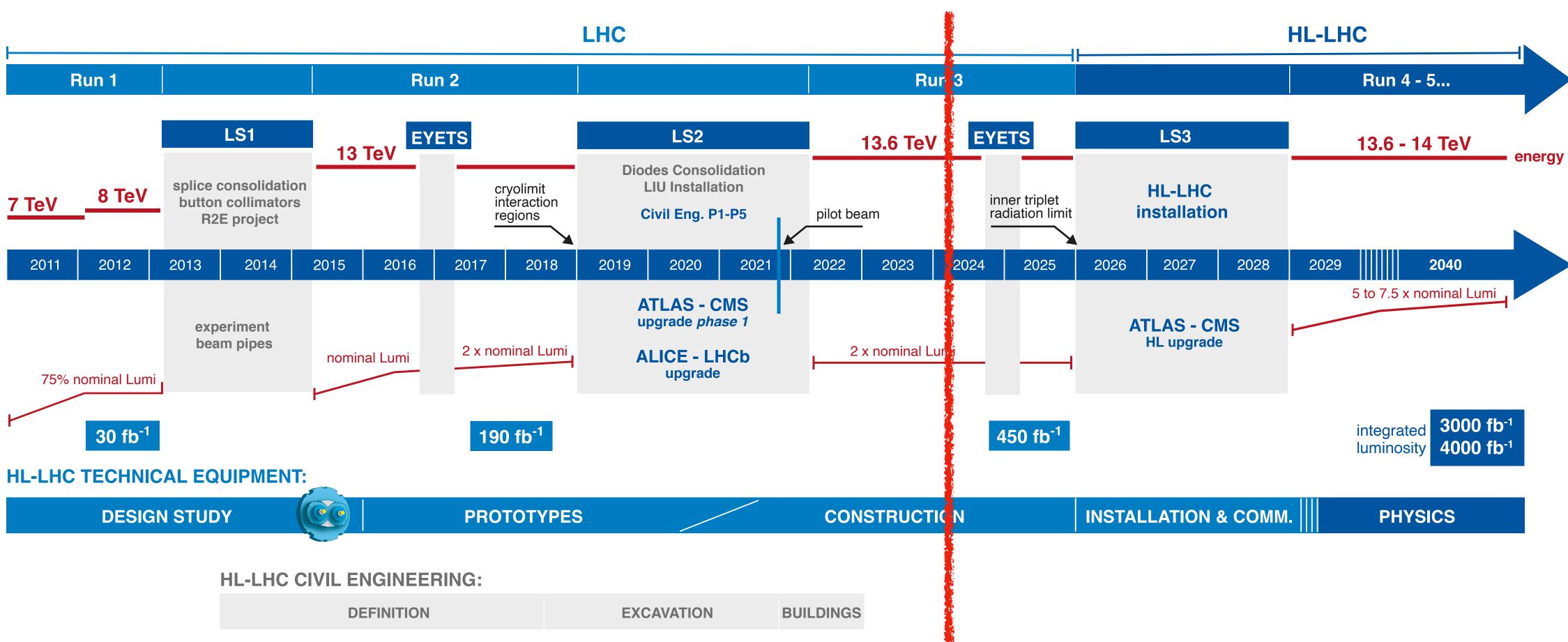

### Data acquisition in CMS during LHC upgrade

Increase of number of collisions -> increase of event complexity and radiation -> need new sub-detectors

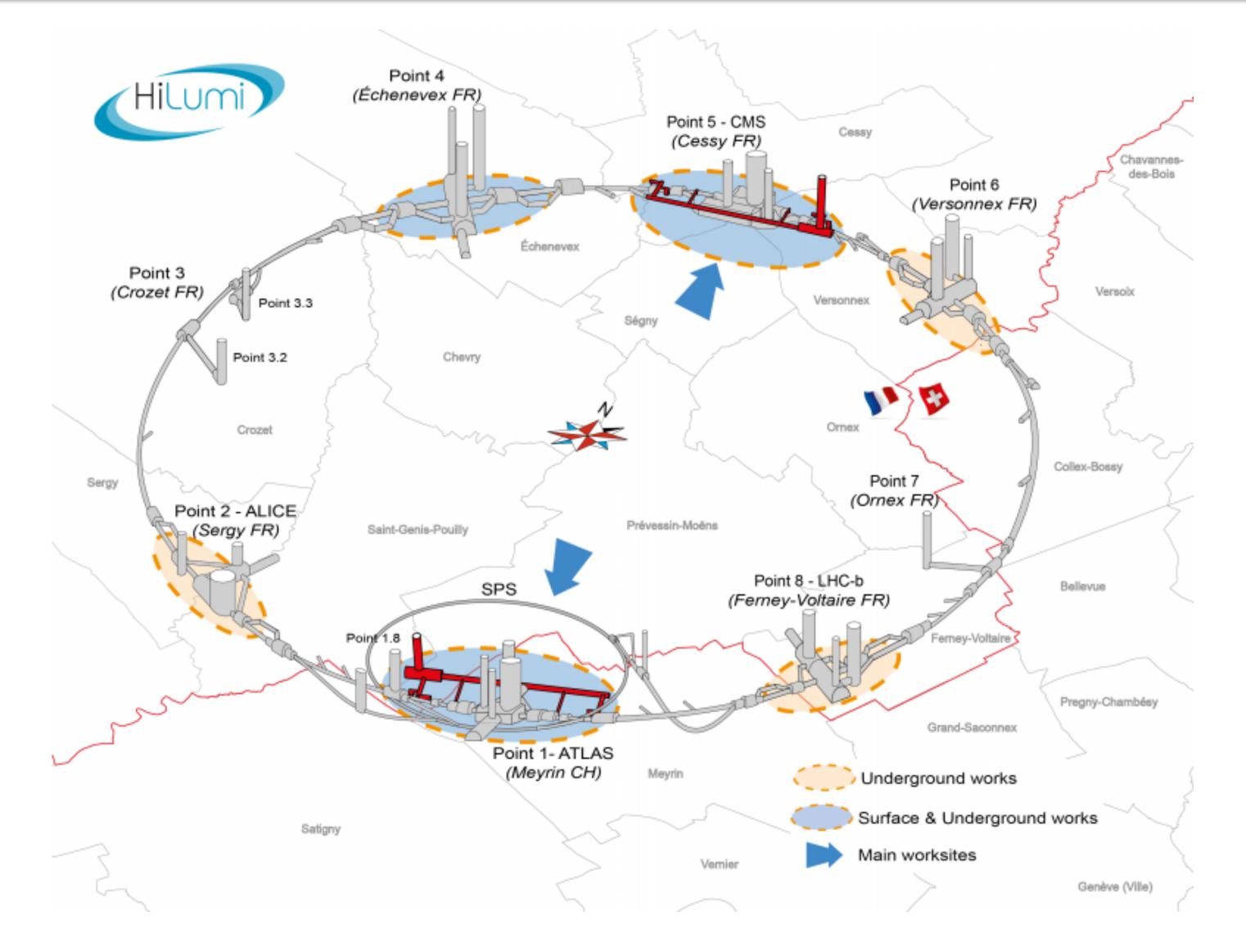

## **HL-LHC Plan**

## **HL-LHC CMS detector overview**

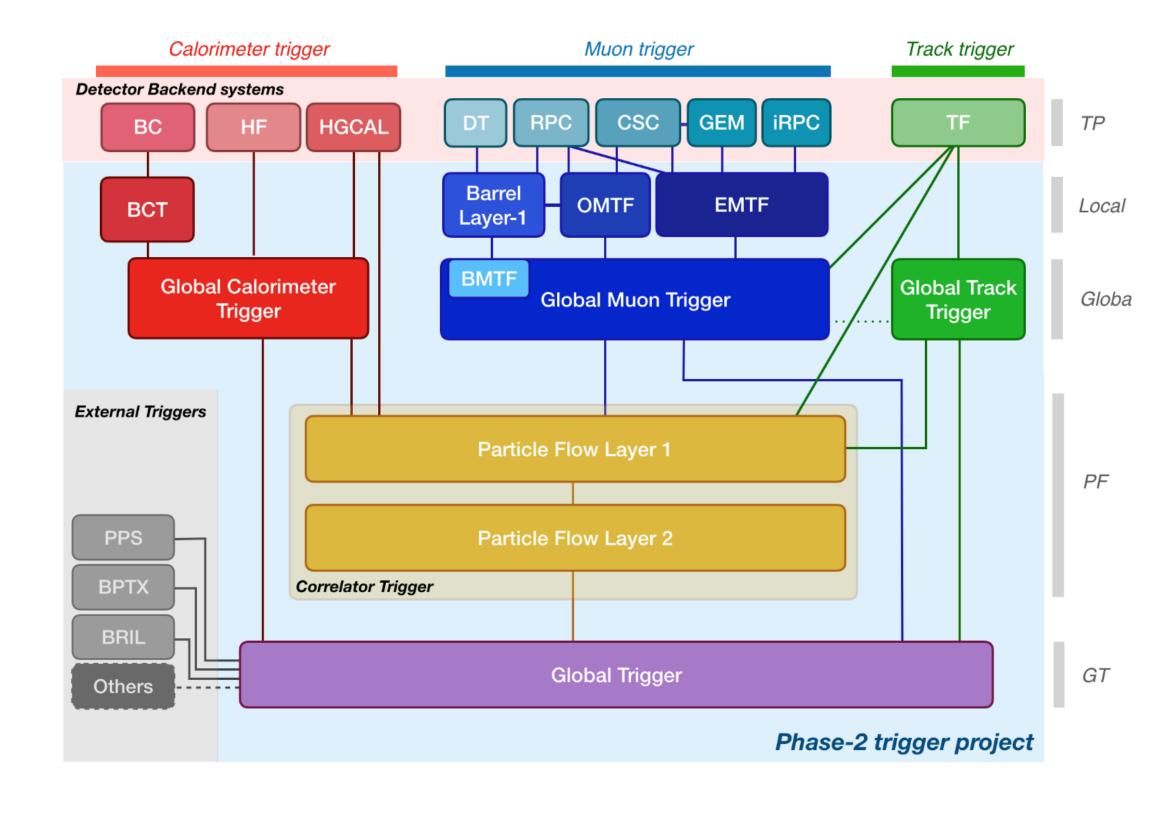

#### L1 Trigger HLT/DAQ

- Tracks in L1-Trigger at 40 MHz

- PFlow selection 750 kHz L1 output

- HLT output 7.5 kHz

- Latency within 12.5 µs

- 40 MHz data scouting

#### **Endcap Calorimeter (HGCAL)**

- 3D showers and precise timing

- Si, Scint+SiPM in Pb/W-SS

#### **Barrel Calorimeter**

- ECAL crystal granularity readout at 40 MHz

- with precise timing for  $e/\gamma$  at 30 GeV

- ECAL and HCAL new Back-End boards

#### **MIP Timing Detector**

- Barrel layer: Crystals + SiPMs

- Endcap layer: Low Gain Avalanche Diodes

#### Tracker

- Increased granularity

- Design for tracking in L1-Trigger

- Extended coverage to  $\eta \simeq 4$

# Muon Systems • DT & CSC new FE/BE readout • RPC back-end electronics • New GEM/RPC $1.6 < \eta < 2.4$ • Extended coverage to $\eta \simeq 3$

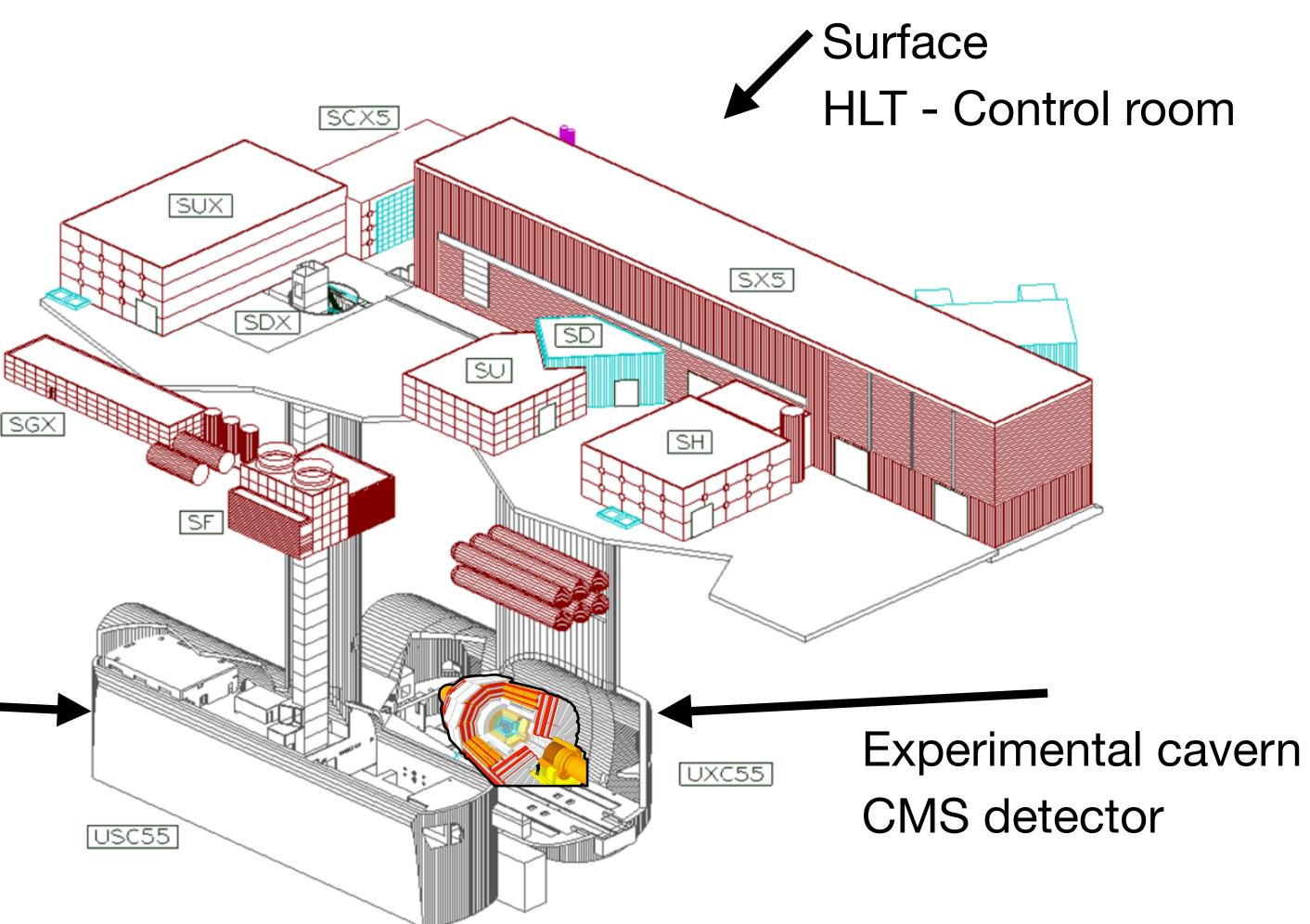

### Service cavern L1 Trigger - DAQ electronics

### **CMS facility - P5**

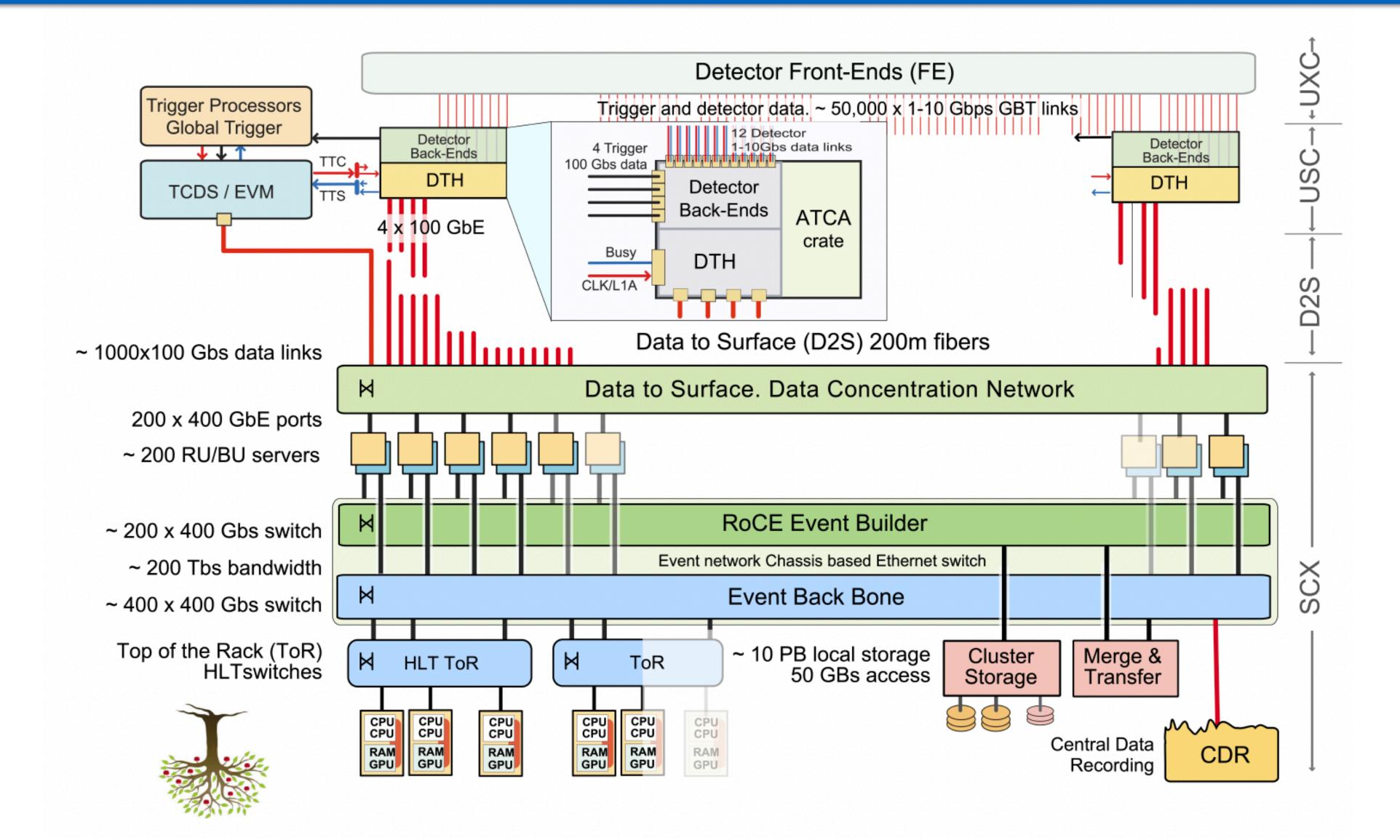

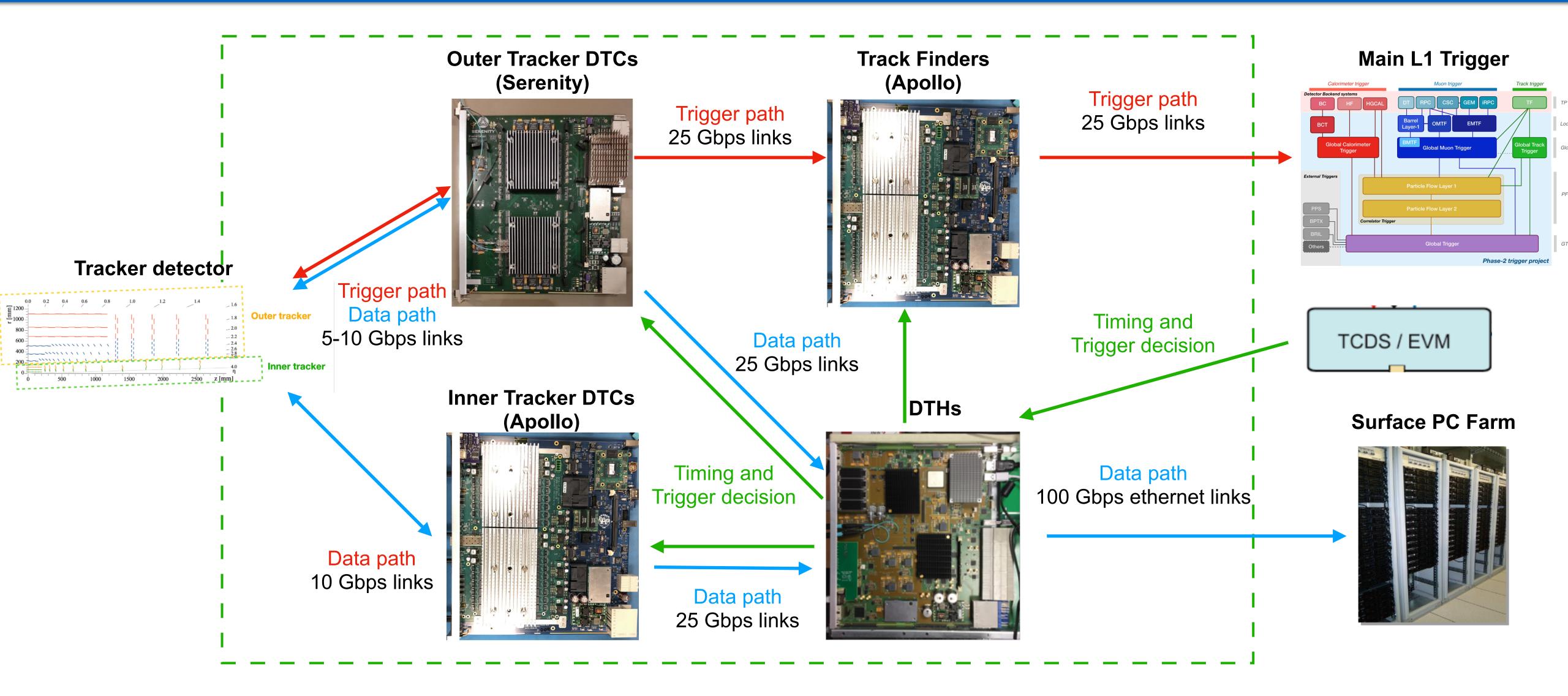

## HL-LHC - CMS T-DAQ

- Output trigger rate 750KHz

- Total maximum latency 12.5 μs

- Particle identification "particle flow" now implemented offline will be implemented in the L1 trigger

- 40 MHz data scouting

- Implemented in ATCA boards using a commercial FPGA (VU13P)

- Some algorithm based on machine learning models developed for FPGAs

- **Track reconstruction** at L1 (not available at present)

## HL-LHC - L1 Trigger

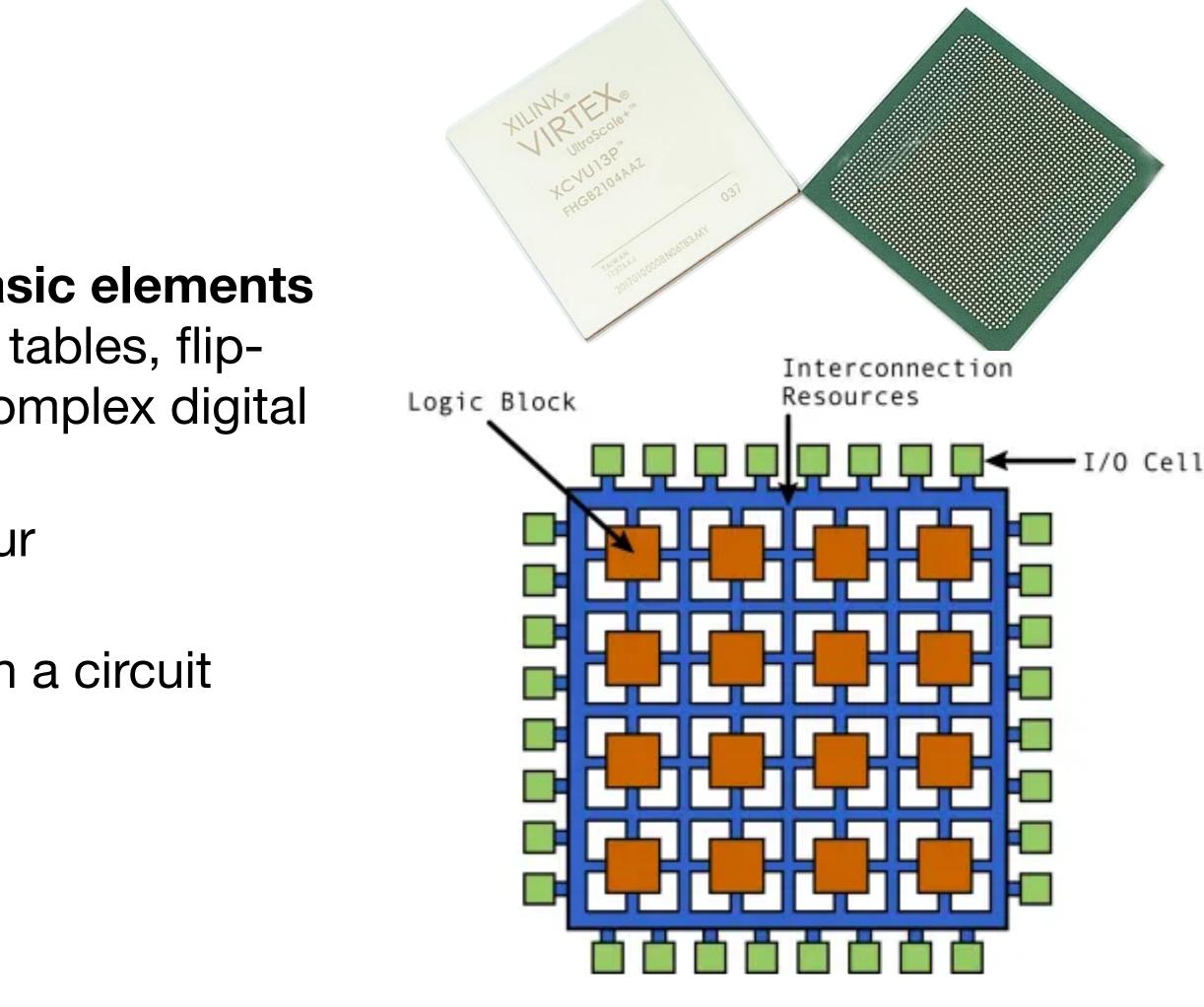

- FPGA: Field Programmable Gate Array

- FPGA is an integrated circuit which contains basic elements of digital (mostly) electronics: memories, lookup tables, flipflops, etc... which can be combined to create complex digital circuits

- It's programmable, you can always change your implementation

- The circuit is implemented into the FPGA trough a circuit description file (in HEP often called "firmware")

### **FPGA 1/2**

Source: Link

- Firmware is generated from a hardware description language (e.g. VHDL)

- Algorithm -> Hardware circuit

- Recently high level languages (C, java) have been interfaced to HDLs to allow a wider audience to program FPGAs, e.g. Xilinx HLS

- Benefits from FPGAs usage in HEP

- Flexibility: the implemented circuit can be changed reprogramming the FPGA

- **Parallelisation**: multiple data processing at the same time

- High data throughput: each FPGA can connect more than 100 high speed links (up to 25 Gb/s per link in our case)

### **FPGA 2/2**

```

1 library ieee;

2 use ieee.std_logic_1164.all;

3 use ieee.numeric_std.all;

5 entity signed_adder is

port

Example of

aclr : in std_logic;

std_logic;

: in

VHDL code

: in

std_logic_vector;

11

std_logic_vector;

: in

12

: out std_logic_vector

13

14 end signed_adder;

15

16 architecture signed_adder_arch of signed_adder is

signal q_s : signed(a'high+1 downto 0); -- extra bit wide

17

18

19 begin -- architecture

assert(a'length >= b'length)

21

report "Port A must be the longer vector if different sizes!"

22

severity FAILURE;

q <= std_logic_vector(q_s);</pre>

23

adding_proc:

25

26

process (aclr, clk)

27

begin

28

if (aclr = '1') then

29

q_s <= (others => '0');

30

elsif rising_edge(clk) then

31

q_s <= ('0'&signed(a)) + ('0'&signed(b));</pre>

32

end if; -- clk'd

33

end process;

34

Source: Wikipedia

35 end signed_adder_arch;

```

- L1 Trigger group is already prototyping the future algorithms

- Strong use of high level language (HLS) to program the FPGA

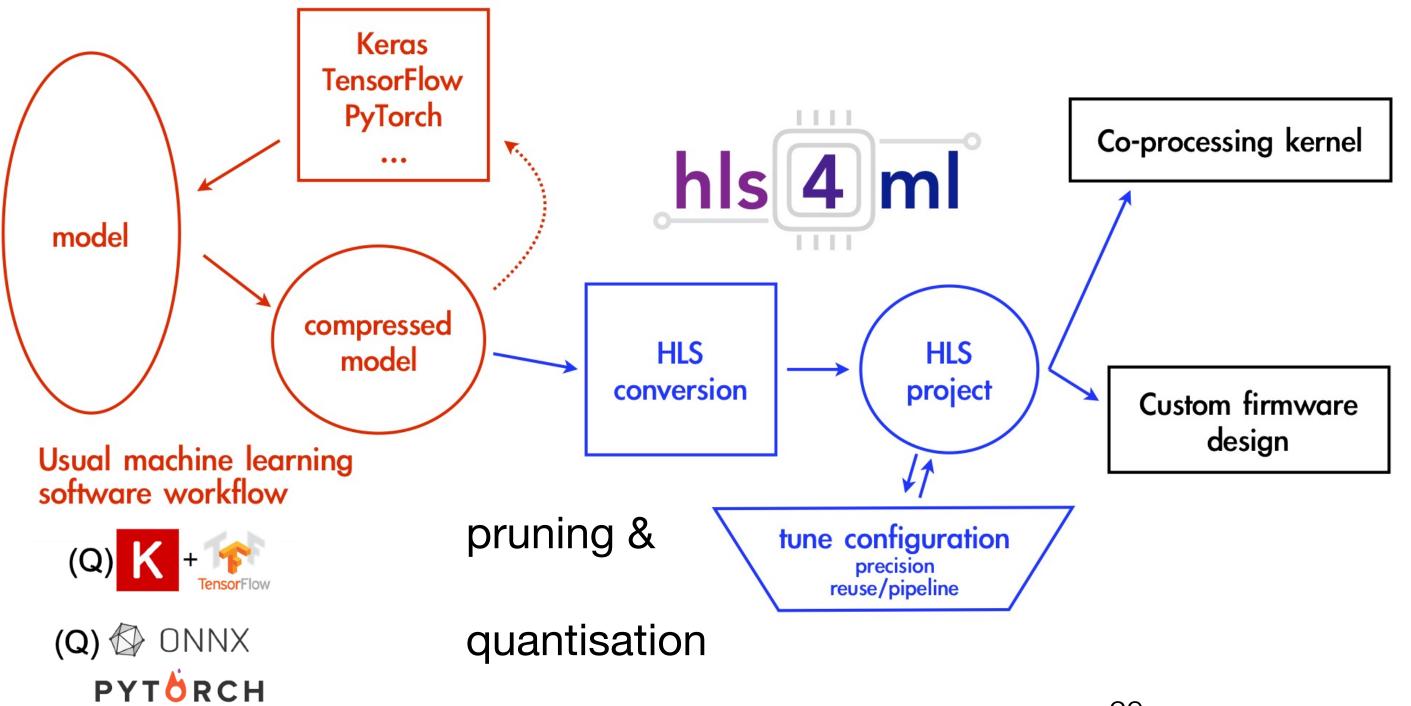

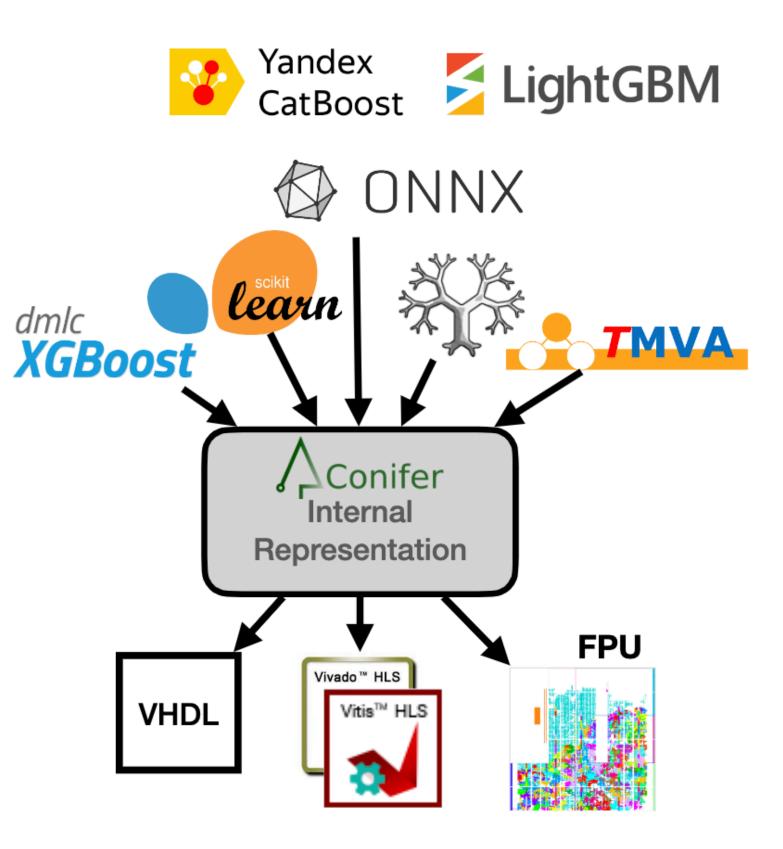

- Implementation of machine learning models into the FPGA: **<u>HLS4ML</u>** and <u>**Conifer**</u> (Decision Forests)

### Machine learning models on FPGAs

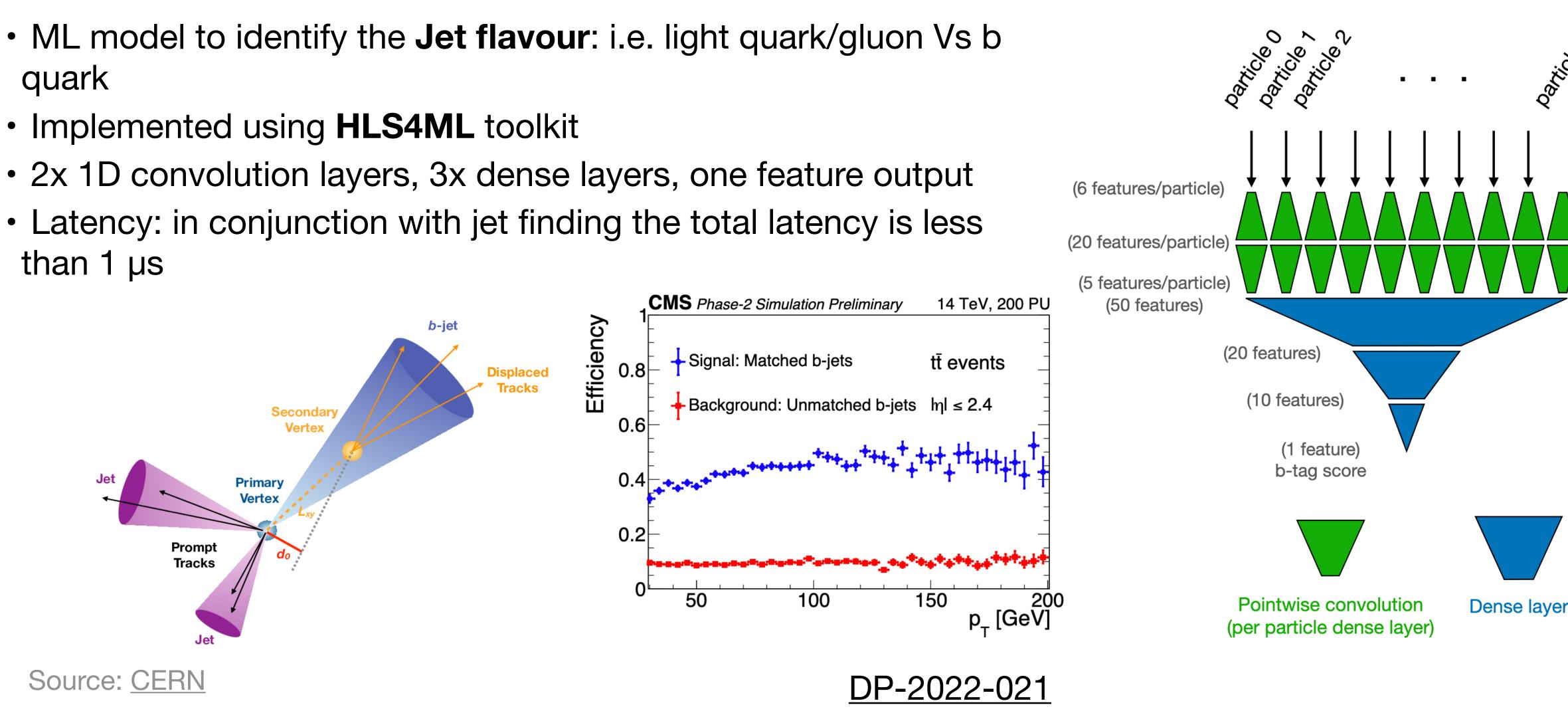

- quark

- Implemented using HLS4ML toolkit

- than 1 µs

### **Example: Jet identification**

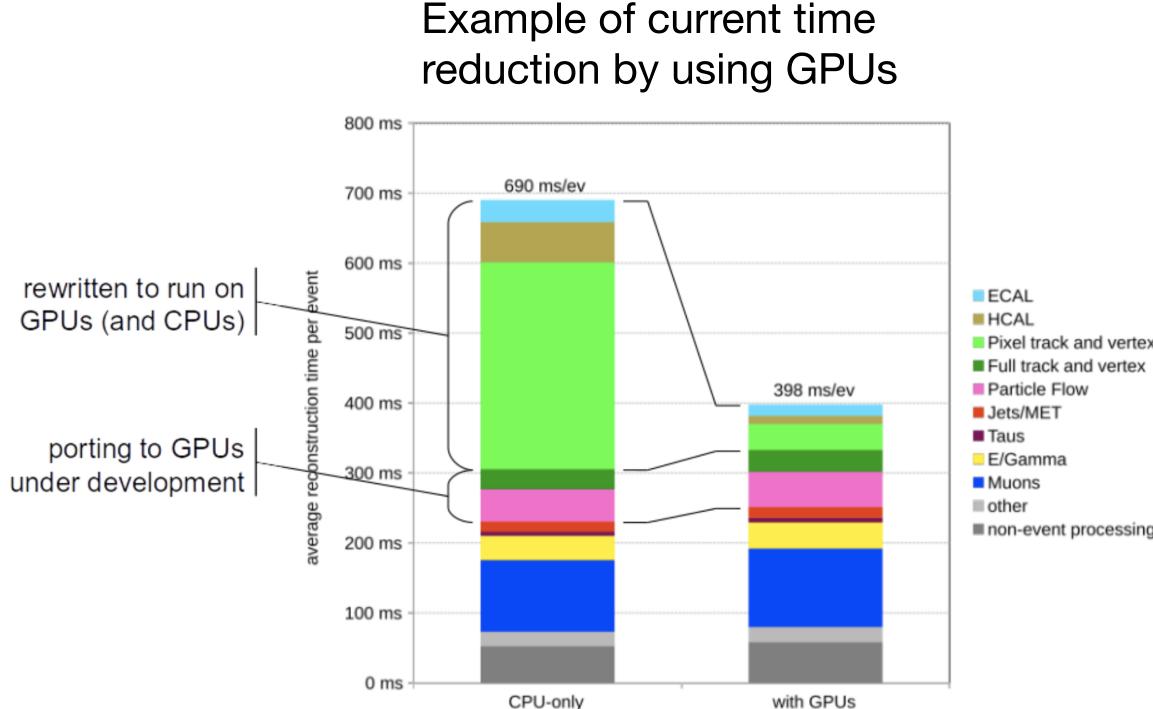

- Event processing 3-4 seconds

- Output trigger rate 7.5 kHz

- Implementation of heterogeneous computing, e.g. GPU (introduced during current data taking), FPGA(?), TPU(?)

- Testing abstraction libraries, e.g. Alpaka

- About 1000 PC in the HLT farm

## **HL-LHC - HLT Trigger**

Source: CERN

### **Focus on CMS Tracker**

### **CMS Tracker subdetector**

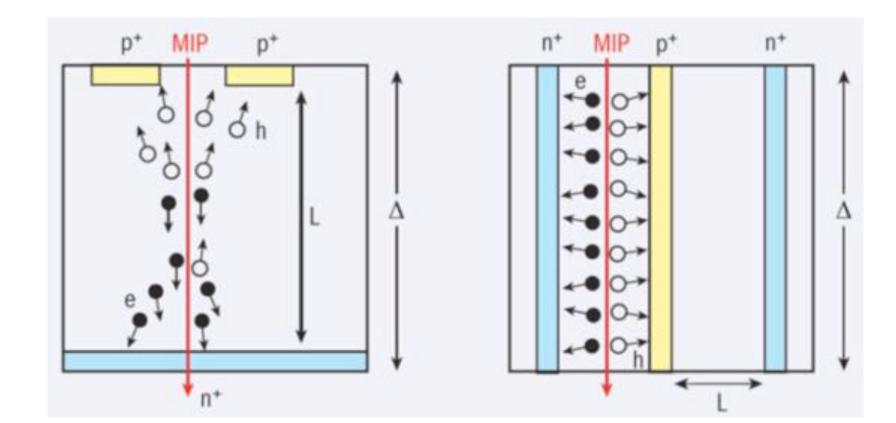

- Detects the passage of charged particles

- With pattern finding and fitting it enables the reconstruction of the trajectory of charged particles

- Thanks to the strong and uniform magnetic filed (3.8T) we can measure their **momentum**

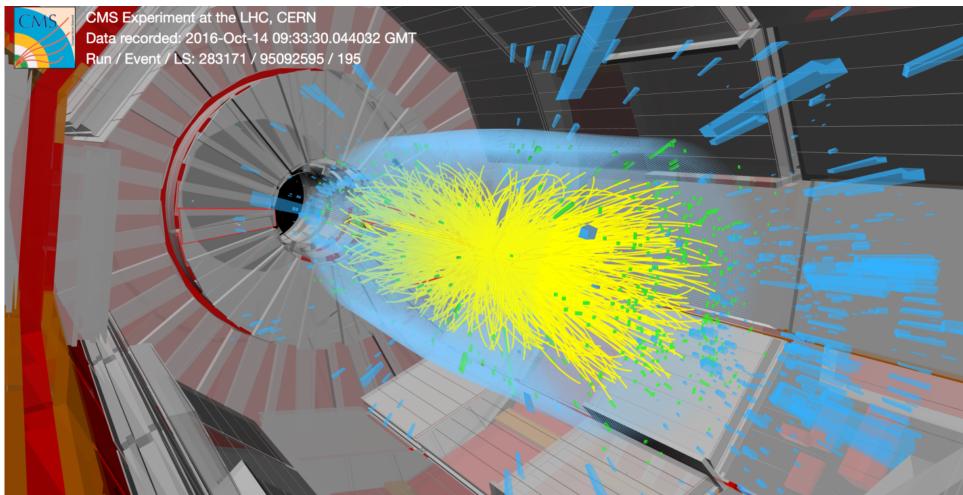

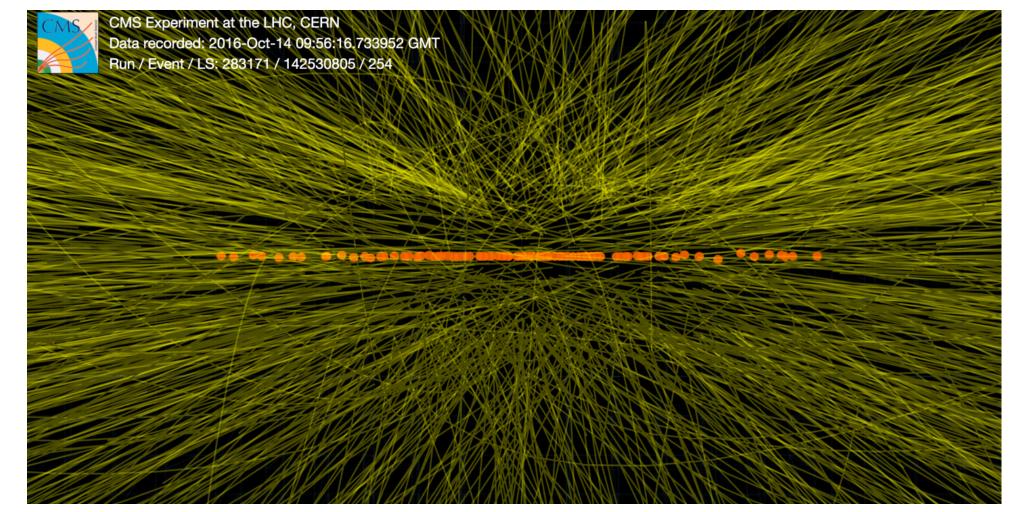

Each bunch crossing generates multiple proton-proton collisions, one collision at most is an interesting event, other collisions constitute "noise" called "pile-up"

During HL-HLC data taking we expect event with pile-up 200 and we want to generate L1 trigger information from the tracker: L1 tracks to be reconstructed within 5 µs

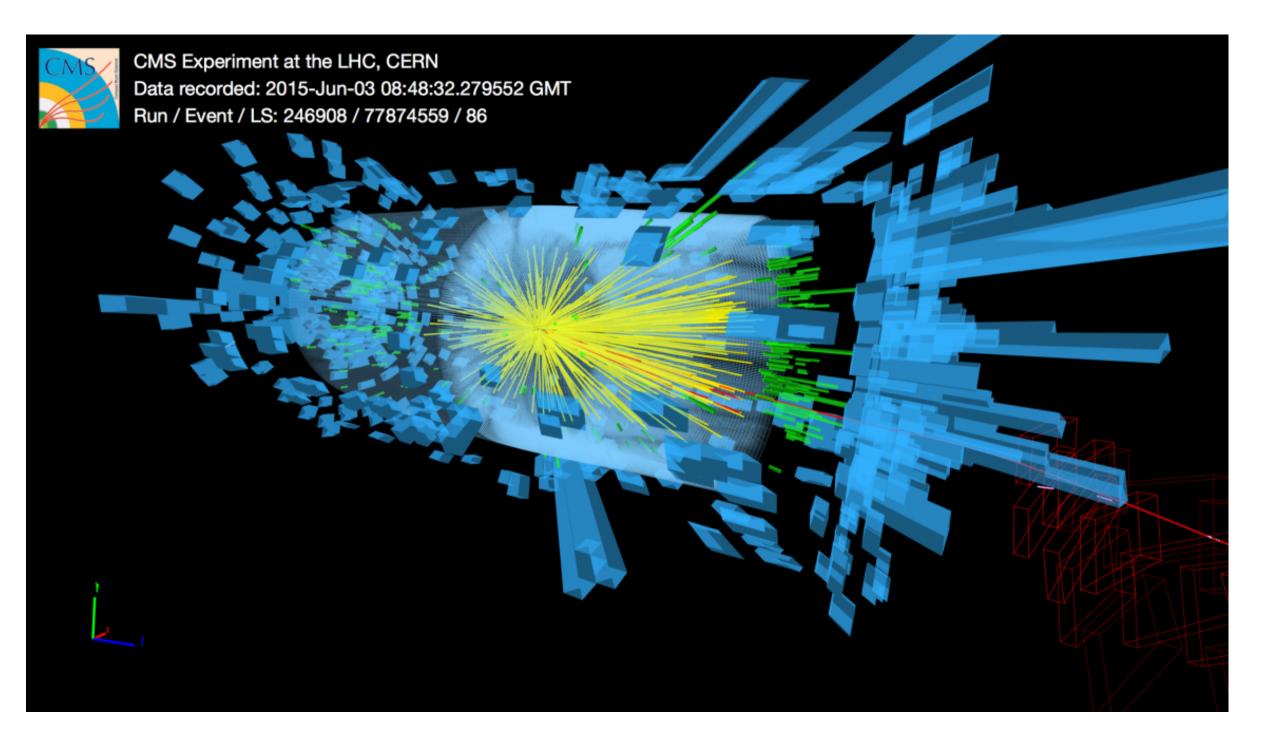

### Event display of a high pile-up event

### The HL-LHC challenge

#### <pile-up> ~ 100

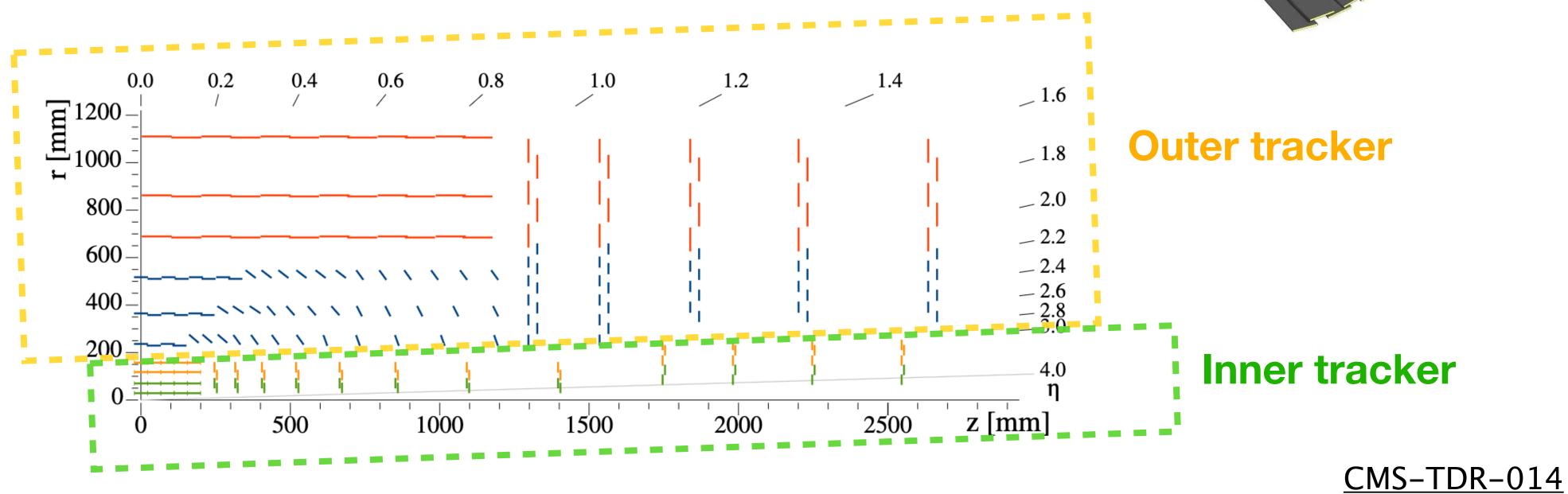

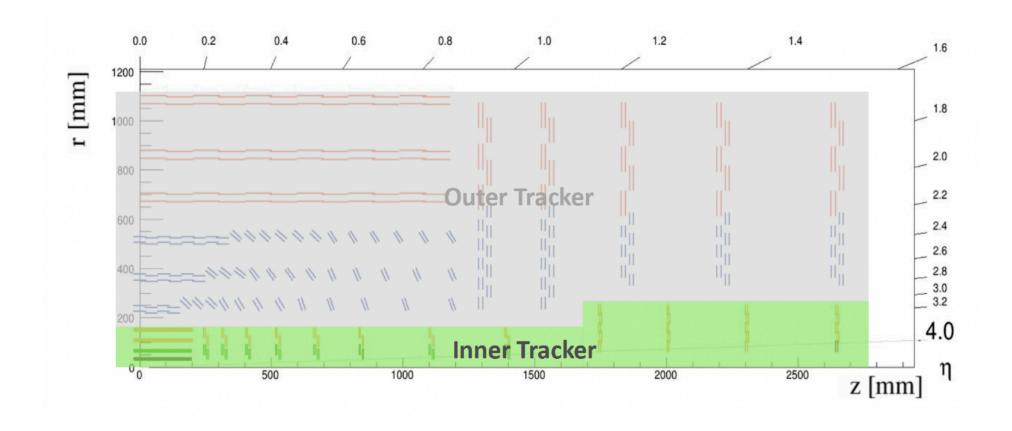

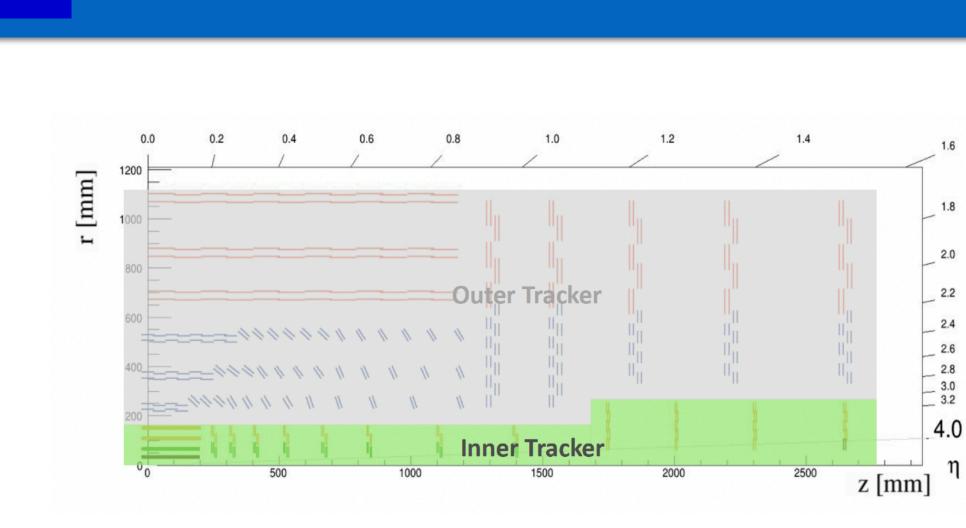

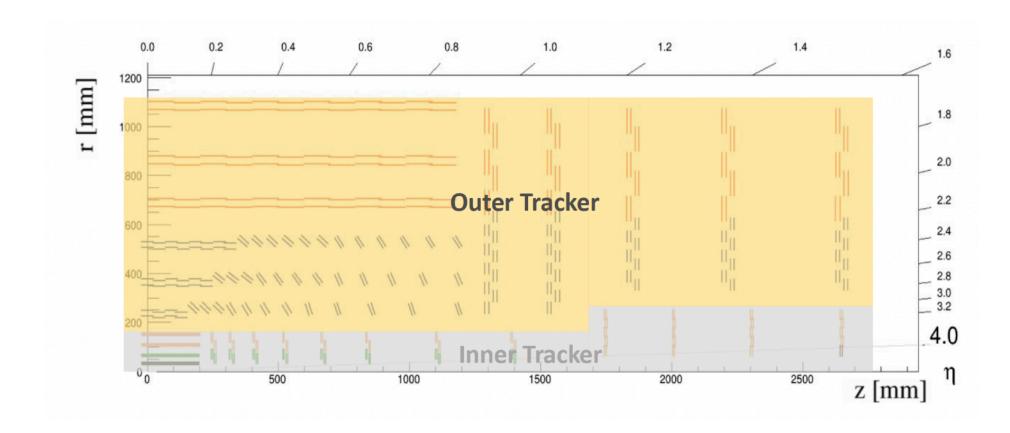

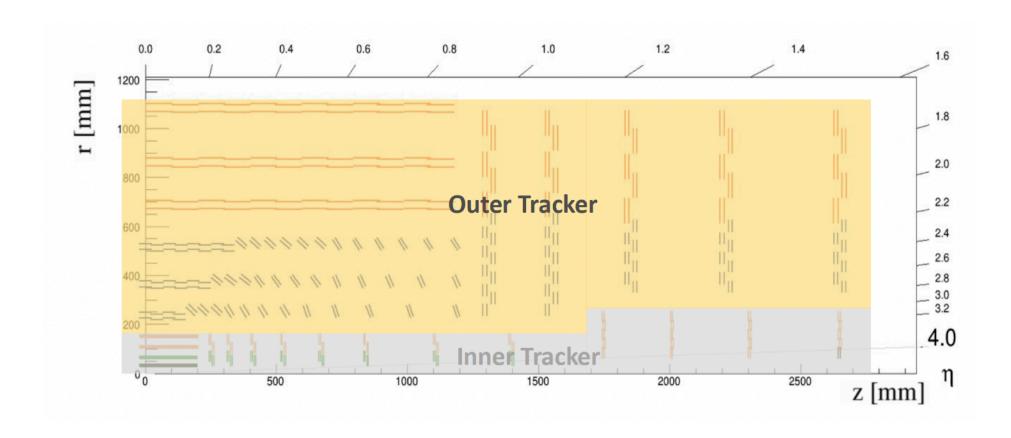

### **HL-LHC CMS Tracker**

General increase of granularity and radiation hardness

### **Some key features**

- Tilted geometry of part of the tracker

- Reduced front-end data rate via in-situ trigger data filtering (pt modules)

- Reconstruction of the **charged particle trajectory** at trigger **Level 1** (hardware trigger) by using the outer tracker data

- Material budget reduction

Heavie

New Pixel Barrel

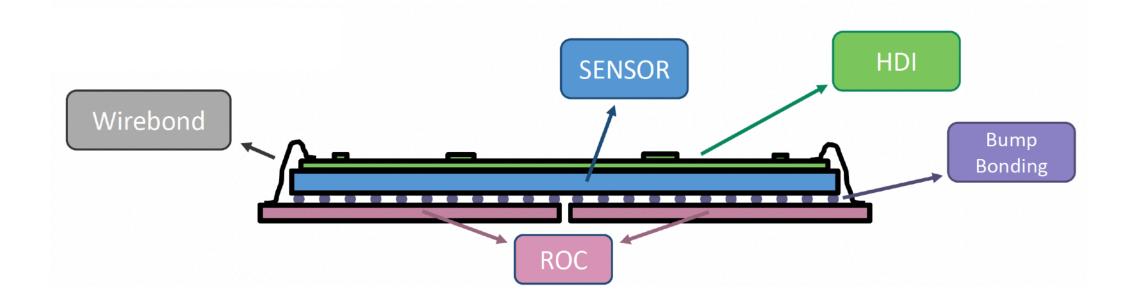

### **Based on silicon pixel sensors**

#### **Modules**

- Two types of Pixel Modules: 1x2 and 2x2 readout chip

- Read Out Chip (ROC) bump bonded on sensor

- Serial powering scheme with up to 11 modules per chain

- 25x100µm<sup>2</sup> pixel cells with 150µm active thickness

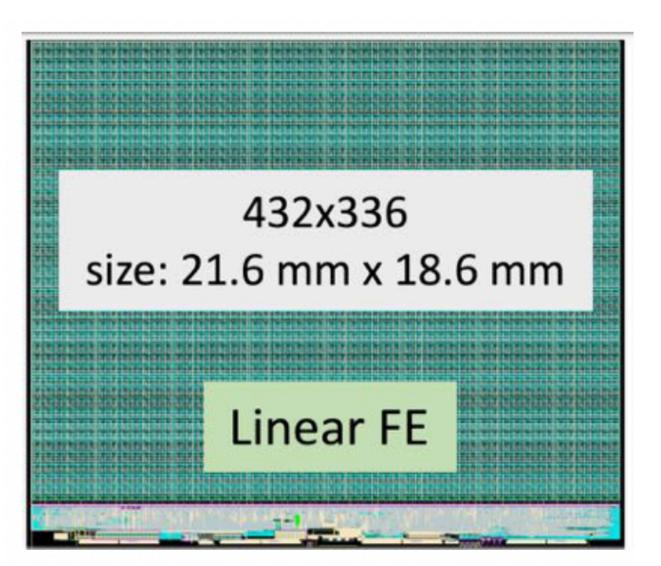

### **HL-LHC Inner Tracker**

## **HL-LHC Inner Tracker - Read-out**

#### **Based on CERN RD53 ASIC project:**

- Based on CMOS 65nm technology

- Radiation tolerant up to 1 Grad

- Low power consumption < 1 W/cm<sup>2</sup>

- Serial powering via on-chip shunt-LDO regulators

- Full size custom chip (ASIC): 432x336 channels

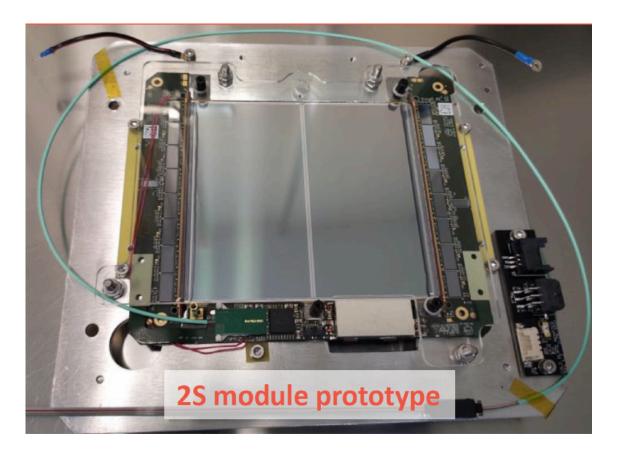

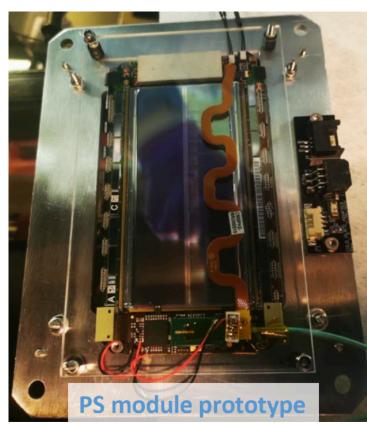

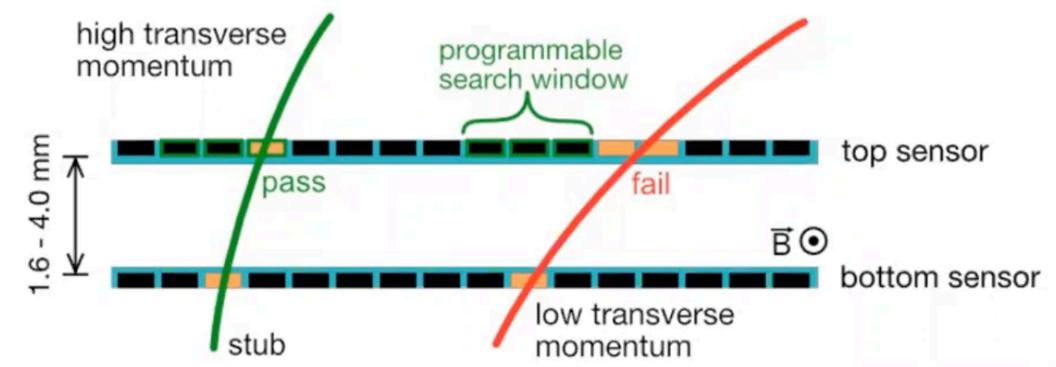

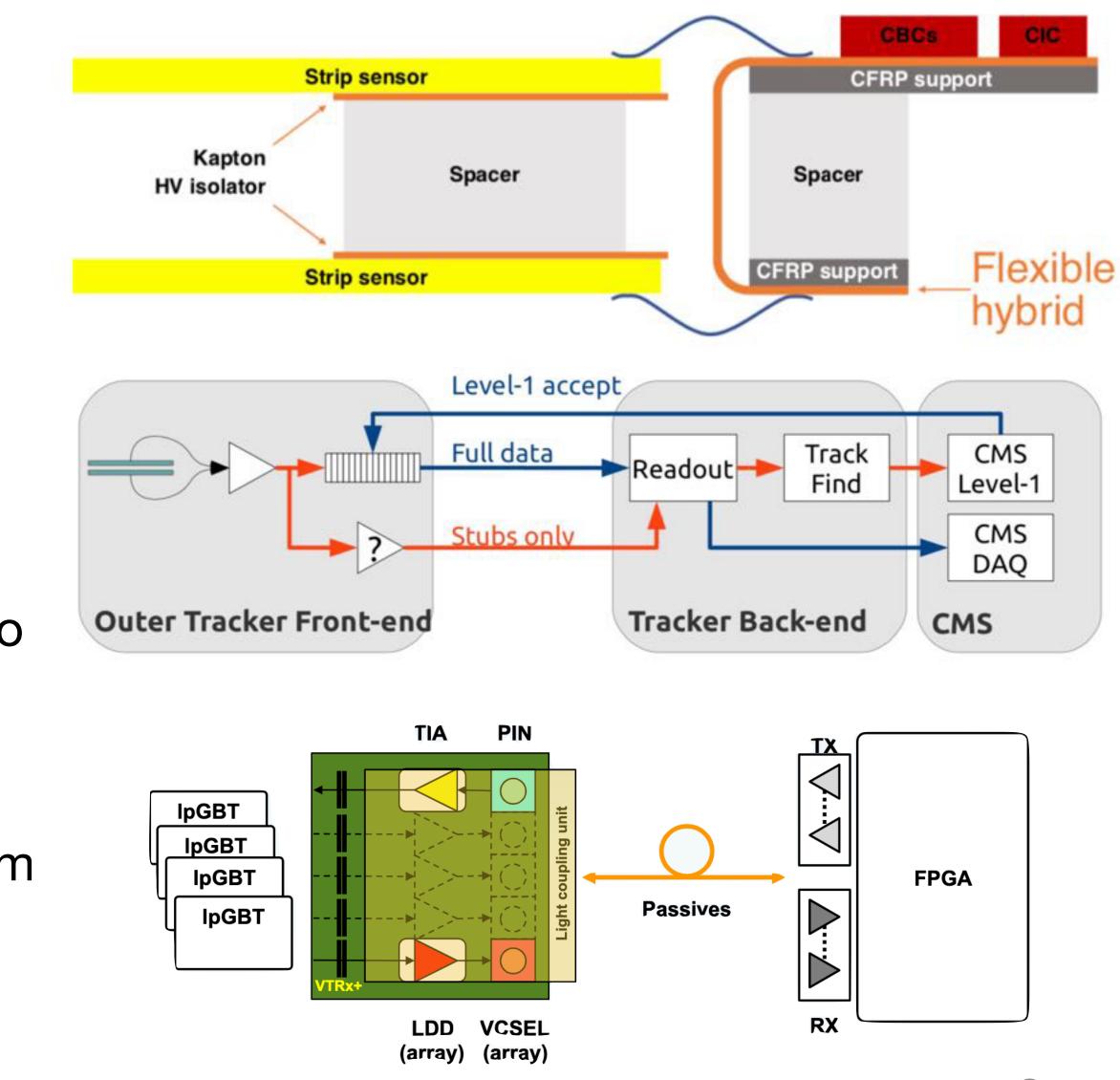

### **Based on silicon strip and strip+pixel sensors**

- •2S modules of 10x10 cm<sup>2</sup>

- PS modules 5x10 cm<sup>2</sup>

- Both types implement a novel idea to reduce the transmitted trigger data: sensor doublet

- Filters out energy deposits not compatible with particle trajectories with pt<2 GeV

- Factor 10 data reduction

### **HL-LHC Outer Tracker**

## HL-LHC Outer Tracker - Read-out

- PS and 2S modules have custom read-out electronics

- Both modules have a common custom chip to gather the information from the read-out chip and receive the L1 Trigger information

- Data is transmitted via optical fibre using a CERN developed driver <u>VTRx+</u> using a custom protocol LpGBT

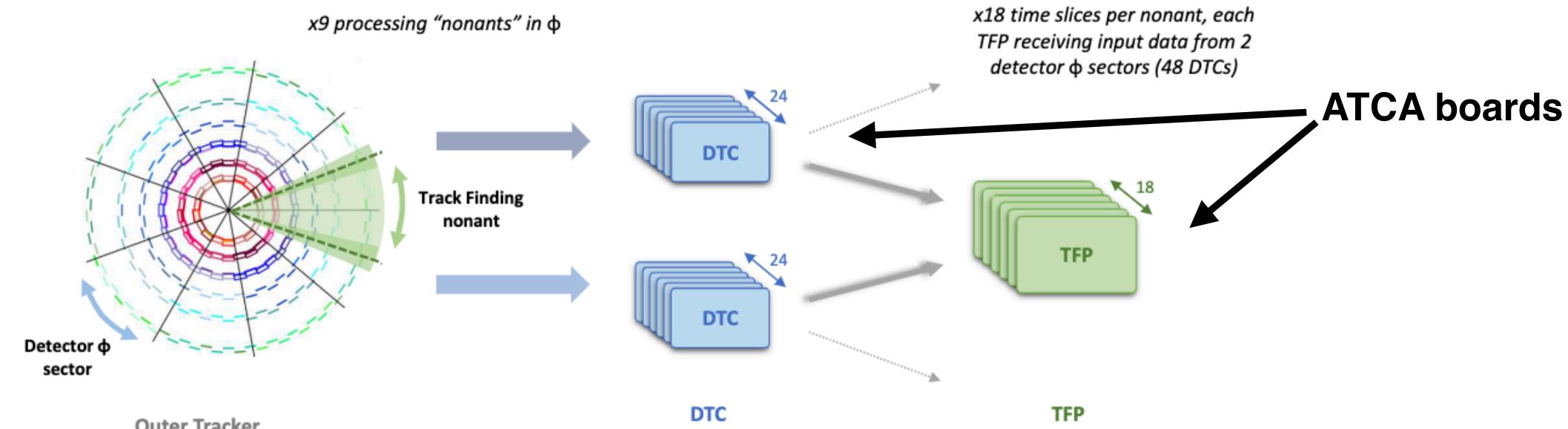

## **HL-LHC Outer Tracker - Trigger path**

**Outer Tracker**

- trigger primitives (tracks)

- Track reconstruction at trigger Level 1 in less than 5 μs

- the track finder board (TFP) with a time multiplexing of x18

- Each TFP board receives an event every 450 ns

Data Trigger & Control

Track Finder Processor

### • Trigger data flows from the front end electronics to the track finder board (TFP) to generate

Data from outer tracker in InI<2.4 are sent to a data carrier board (DTC), which sends the data to

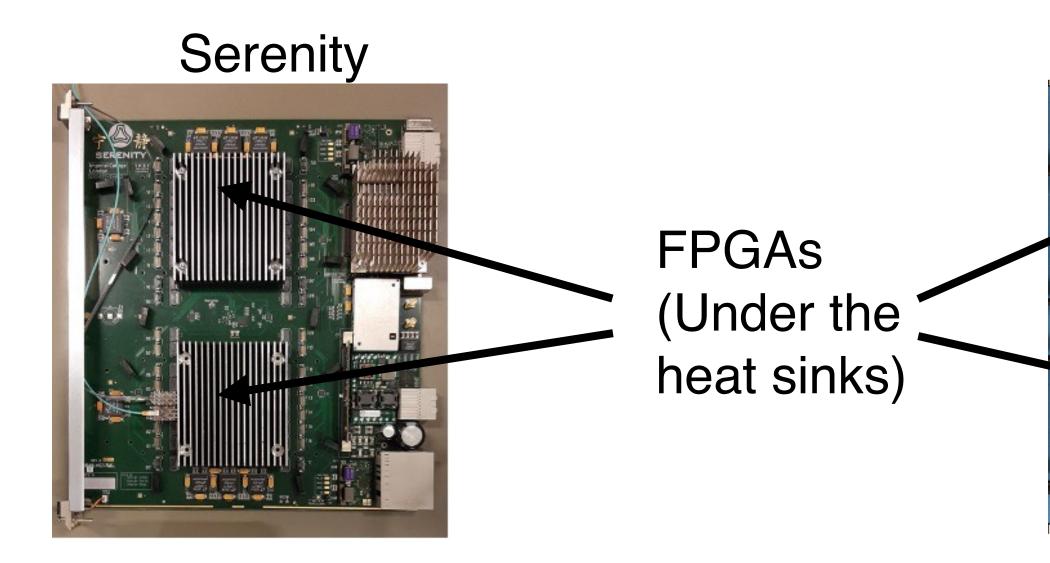

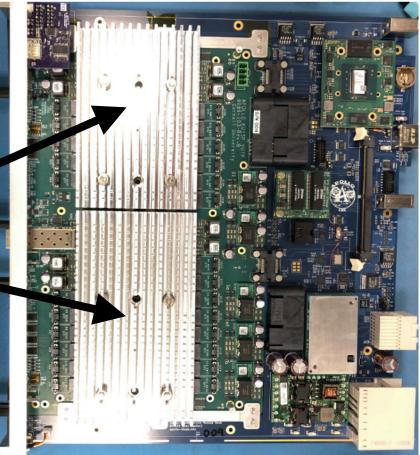

- Based on Advanced Telecommunication Computing Standard: ATCA

- Each board is 280 mm deep and 322 mm high

- All the **back-end systems** and **L1 Trigger** will be implemented in ATCA boards

- Boards are installed in a 14-slot ATCA crate

- Tracker back-end will use custom **ATCA boards**:

- Serenity: Outer Tracker DTC

- Apollo: Inner Tracker DTC and TFP

- **DTH**: Data concentrator, and timing/trigger deliverer

### **ATCA boards**

Apollo

DTH

#### Source: <u>CMS</u>

## HL-LHC CMS Tracker data acquisition

problem

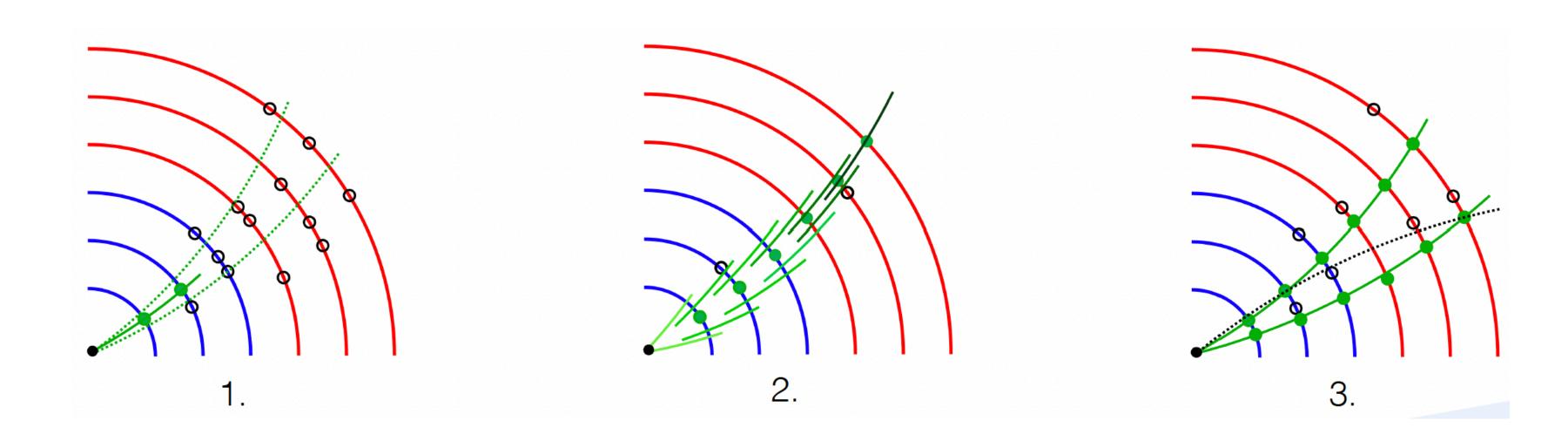

### **Algorithm under development: Tracklet + Kalman filter**

- 1. Pattern based on "tracklet" seeding

- 2. Kalman filter for identify best stub candidates and track parameters

- 3. Boost decision tree to evaluate track quality

## Track Trigger Algorithm

### Each event could have 10k stubs and O(100) reconstructed tracks $\rightarrow$ harsh combinatoric

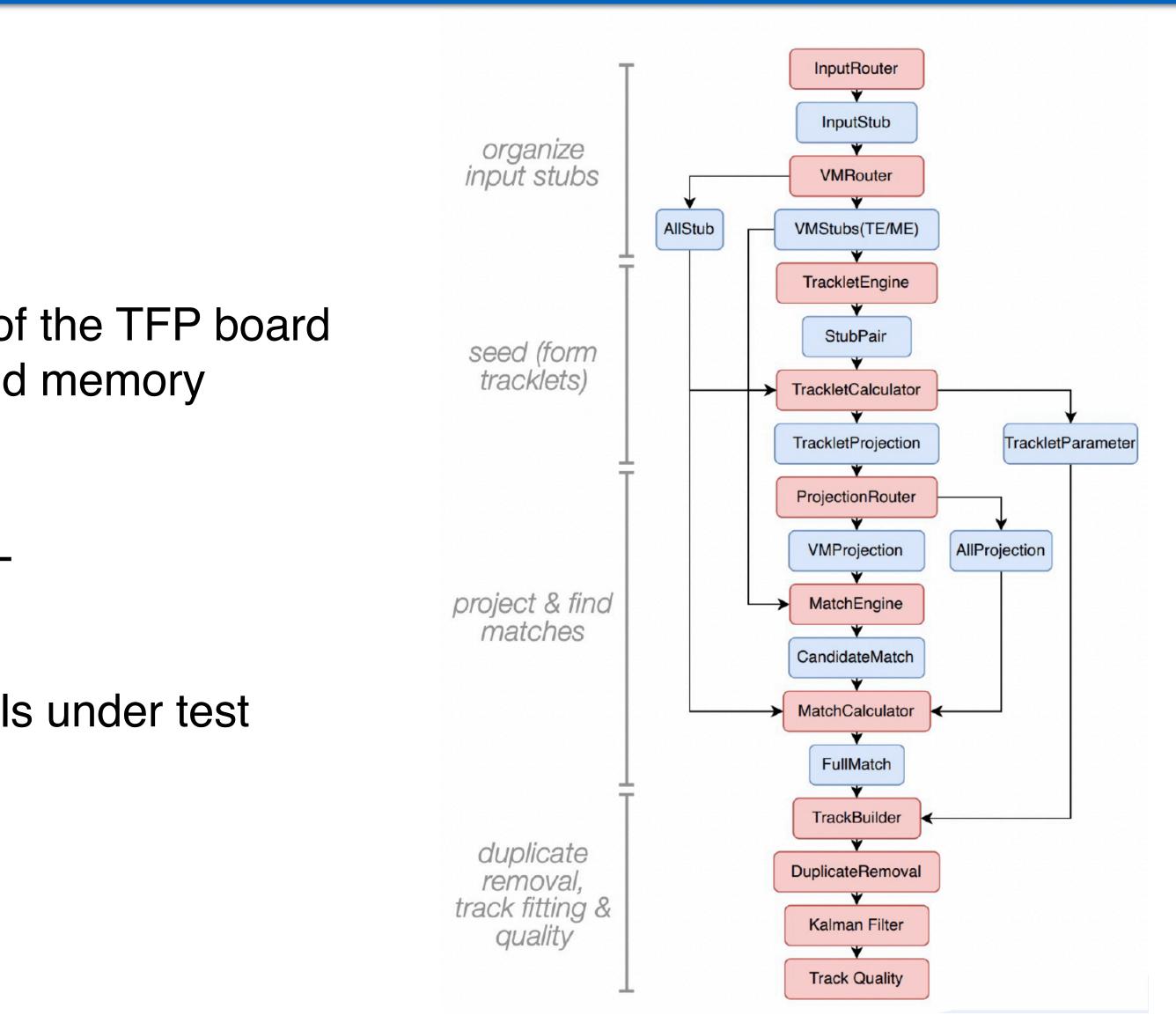

- Implemented in HLS and VHDL in the FPGA of the TFP board

- Pipeline made of processing modules (red) and memory modules (blue)

- Horizontal scalability (parallelisation)

- Kalman filter and Track quality written in VHDL

- Targeting 240 MHz

- Full algorithm needs two VU13P FPGA

- Implementation of some stages with ML models under test

## **Track Trigger Algorithm Firmware**

### **Track Fitter Performance**

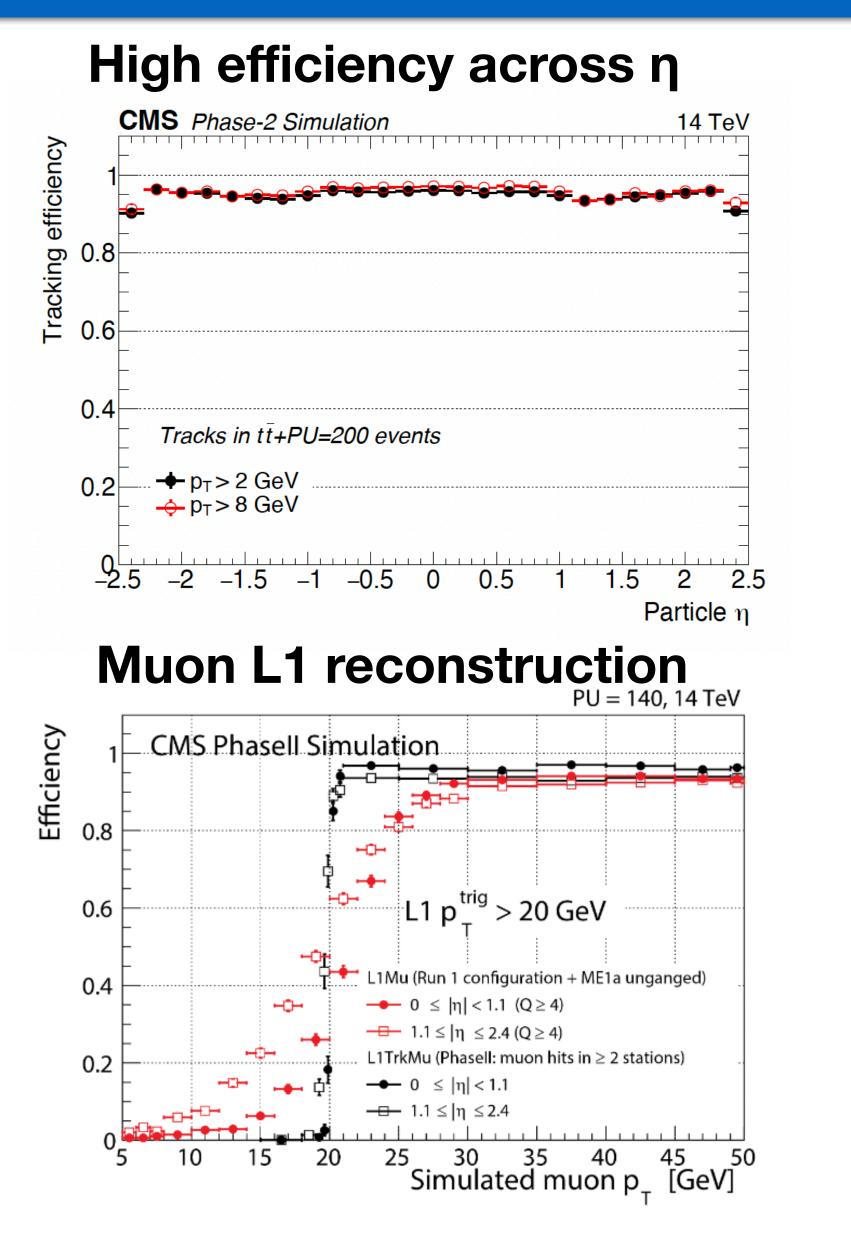

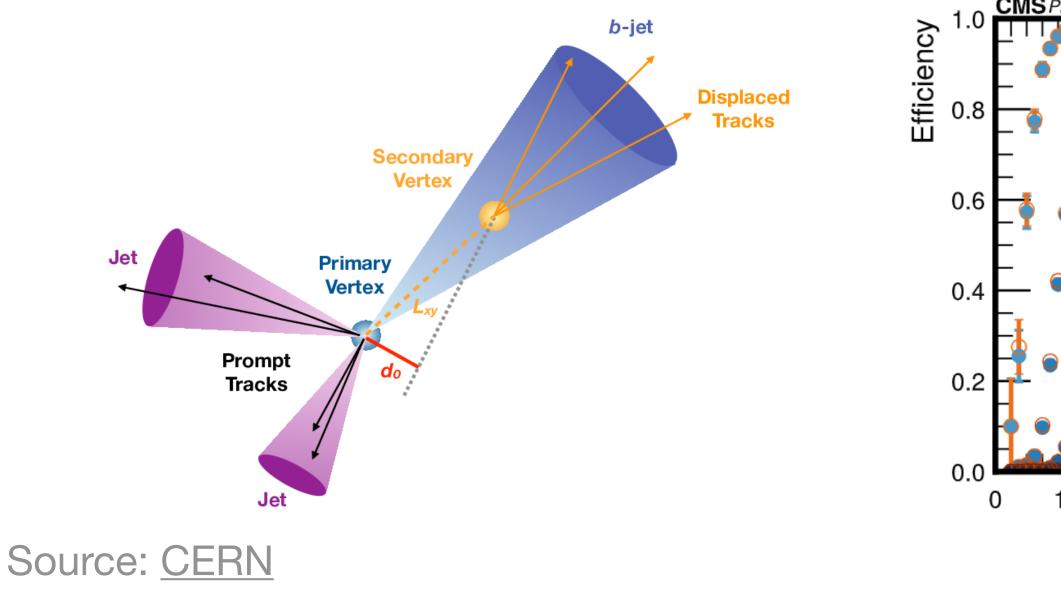

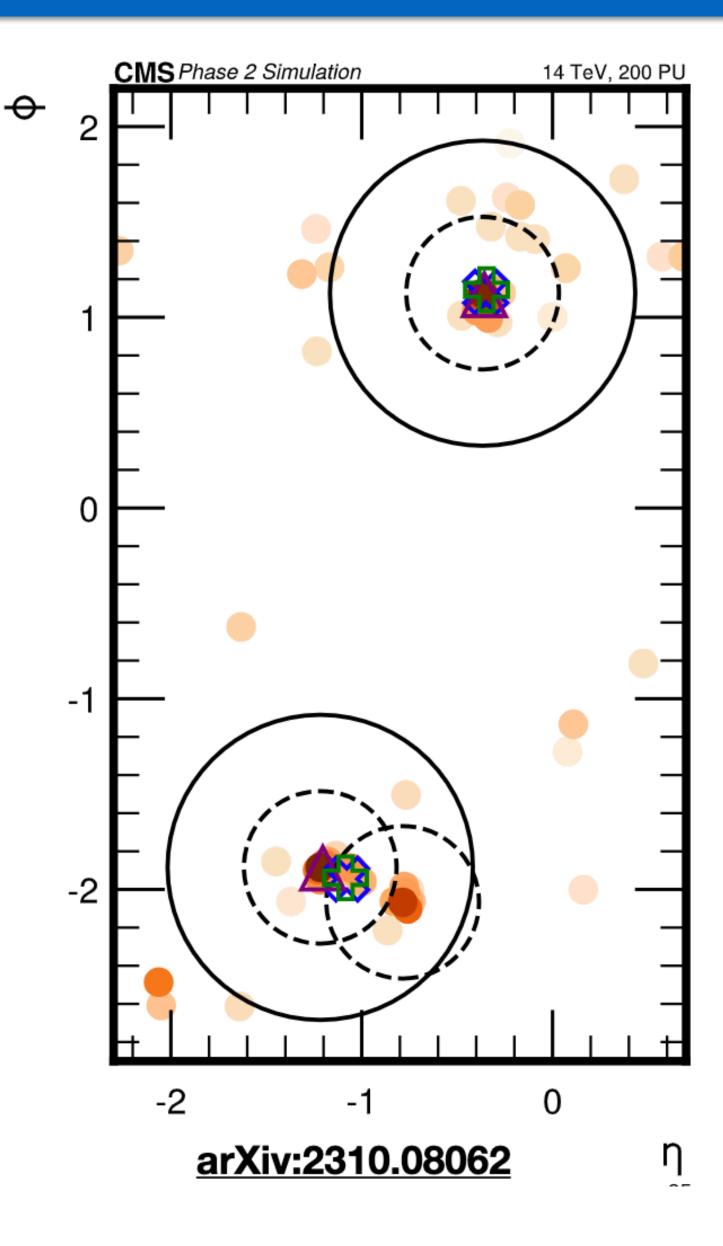

• The reconstruction of tracks in L1 Trigger at HL-LHC allows to keep good detector performance in the presence of high pile-up Primary vertices, jets reconstruction at L1

• Better resolution, e.g. for muons, implies lower trigger t

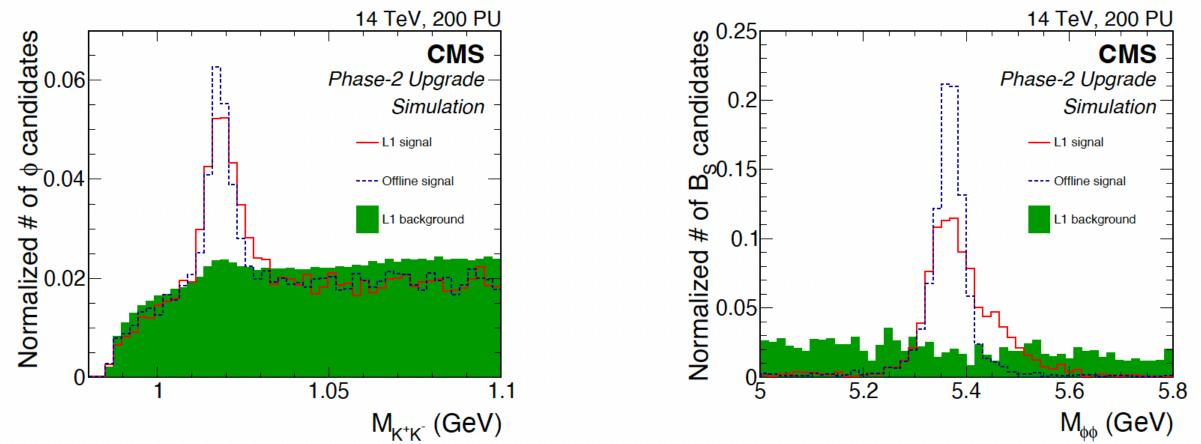

#### Give access to hadronic channels: e.g. $\phi \rightarrow KK$ , thus to $B_s \rightarrow \phi \phi$

- The data acquisition system is fundamental in each HEP experiment • LHC provides high proton bunch collision rate which generates high data

- volumes

- A two-level triggering system is used to find the signature of interesting physics events

- In 2029 LHC will start a new phase with higher luminosity (higher number of collisions per bunch crossing)

- CMS will update all the sub-detectors and the data acquisition system to cope with the higher pileup

- Details of the future Tracker acquisition system have been shown

### **Additional slides**

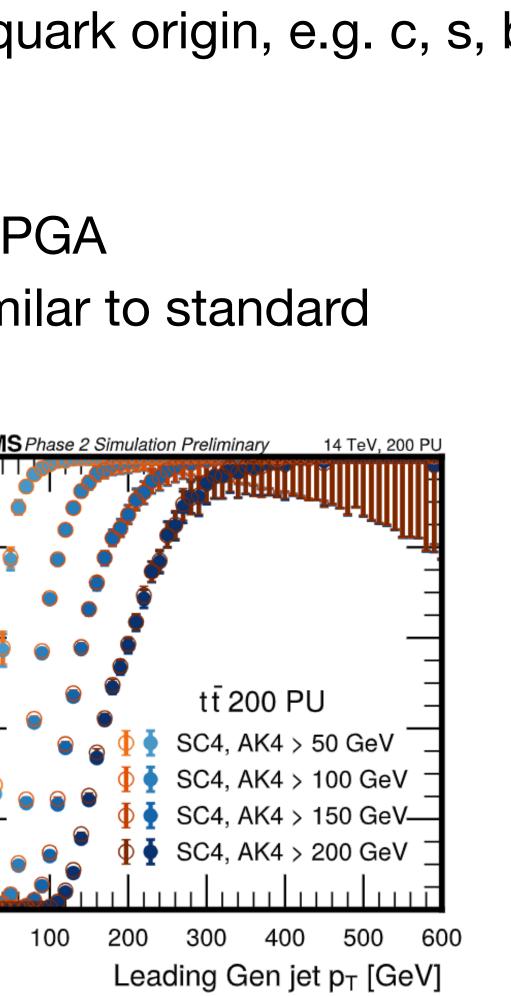

- Clustering of particles into jets and tag the quark origin, e.g. c, s, b, etc

- Implemented using HLS4ML toolkit

- Fast and performant jet reconstruction for FPGA

- Latency: 750 ns for 12 jets, performance similar to standard algorithm

### **Example: Jet Reconstruction**

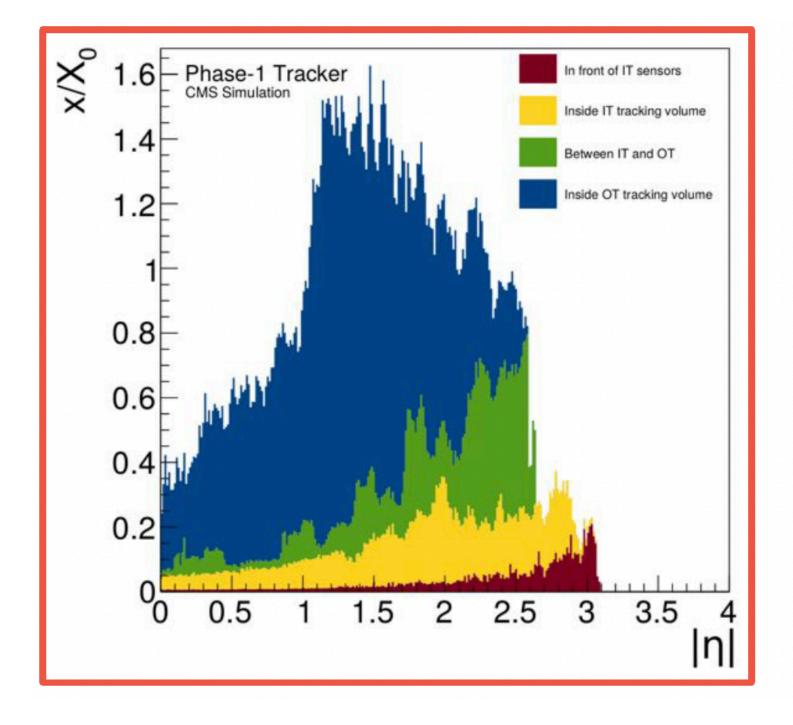

### Tracker material budget

### HL-LHC